- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: iMX8QM DDR memory space and configuration suggestions

iMX8QM DDR memory space and configuration suggestions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone,

Here are some questions I would like to ask about LPDDR4 for iMX8QM, please help to confirm.

1. I would like to understand how much DDR memory space can be supported up? It doesn't seem to be mentioned in the datasheet.

2. Our motherboard has 8GB memory requirement, would you recommend us to use the LPDDR4 configuration of 8GB*1 or 4GB*2?

3. Is there any LPDDR AVL here that can provide us with reference?

Thank you.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is a list of maximum supported LPDDR4 memory on the i.MX 8QM / 8X / 8XL:

| SoC | Package | Max data bus width | Maximum density | Assumed memory organization | Notes |

| i.MX 8QM/8QP | 29x29 mm | 32-bit (per controller) | 32Gb/4GB (per controller) | dual rank, dual-channel device with 16-row addresses (R0-R15) | 1, 2, 4 |

| i.MX 8QXP/8DXP | 21x21 mm | 32-bit | 32Gb/4GB | dual rank, dual-channel device with 16-row addresses (R0-R15) | 1, 2, 4 |

| i.MX 8QXP/8DXP | 17x17 mm | 16-bit | 16Gb/2GB | dual rank, single-channel device with 16-row addresses (R0-R15) | 1, 2, 3, 4, 9 |

| i.MX 8DX | 21x21 mm | 16-bit | 16Gb/2GB | dual rank, single channel device with 16-row addresses (R0-R15) | 1, 2, 3, 4, 9 |

| i.MX 8DX | 17x17 mm | 16-bit | 16Gb/2GB | dual rank, single channel device with 16-row addresses (R0-R15) | 1, 2, 3, 4, 9 |

| i.MX 8DXL/8SXL | 15x15 mm | 16-bit | 32Gb/4GB | dual rank, single channel device with 17-row addresses (R0-R16) | 1, 2, 3, 9 |

Note 1:

The numbers are based purely on the IP vendor documentation for the DDR Controller and the DDR PHY, on the settings of the implementation parameters chosen for their integration into the SoC, and on the JEDEC standard JESD209-4A. Therefore, they are not backed by validation, unless said otherwise and there is no guarantee that apart with the specific density and/or desired internal organization is offered by the memory vendors. Should the customers choose to use the maximum density and assume it in the intended use case, they do it at their own risk.

Note 2:

Byte-mode LPDDR4 devices (x16 channel internally split between two dies, x8 each) of any density are not supported therefore, the numbers are applicable only to devices with x16 internal organization (referred to as "standard" in the JEDEC specification).

Note 3:

The memory vendors often do not offer so many variants of the single-channel memory devices. As an alternative, a dual-channel device with only one channel connected may be used. For example:

A dual-rank, single-channel device with 16-row address bits has a density of 16Gb. If such a device is not available at the chosen supplier, a dual-rank, dual-channel device with 16-row address bits can be used instead. This device has a density of 32 Gb however since only one channel can be connected to the SoC, only half of the density is available (16 Gb).

Usage of more than one discrete memory chip to overcome market constraints is not supported since only point-to-point connections are assumed for LPDDR4.

Note 4:

Devices with 17-row addresses (R0-R16) are not supported by the SoCs.

Note 5:

The numbers are based purely on the IP vendor documentation for the DDR Controller and the DDR PHY, on the settings of the implementation parameters chosen for their integration into the SoC and on the JEDEC standard JESD79-3E/JESD79-3F Therefore, they are not backed by validation, unless said otherwise and there is no guarantee that a part with the specific density and/or desired internal organization is offered by the memory vendors. Should the customers choose to use the maximum density and assume it in the intended use case, they do it at their own risk.

Note 6:

The density can be achieved by connecting 8 single rank discrete devices with one 8Gb die each, 4 devices connected to each chip select or by connecting 4 dual rank discrete devices with two 8Gb dies each. Note that this number of discrete devices significantly exceeds the number of devices used on the validation board (2 discrete devices, not taking into account the device used for ECC) therefore, it is not guaranteed that the i.MX would be able to drive the signals with margin to the required voltage levels due to increased loading on the traces. Significant effort would be required in terms of PCB layout and signal integrity analysis. Practically, it is not recommended to use more than 2 discrete DDR3L devices. This corresponds to the maximum density of 16Gb/2GB in case of the single rank devices containing one 8Gb die or 32Gb/4GB in case of the dual-rank devices containing two 8Gb dies (x16 8Gb devices with 16-row addresses and 10 column addresses assumed instead of x8 devices in such case).

Note 7:

The density can be achieved by connecting 4 single rank discrete devices with one 8Gb die each, 2 devices connected to each chip select or by connecting 2 dual rank discrete devices with two 8Gb dies each. Note that the first option exceeds the number of devices used on the validation board (2 discrete devices) therefore, it is not guaranteed that the i.MX would be able to drive the signals with margin to the required voltage levels due to increased loading on the traces. Significant effort would be required in terms of PCB layout and signal integrity analysis. Practically, it is not recommended to use more than 2 discrete DDR3L devices. This corresponds to the maximum density of 16Gb/2GB in case of the single rank devices containing one 8Gb die or 32Gb/4GB in case of the dual-rank devices containing two 8Gb dies.

Note 8:

The density can be achieved by connecting 2 single rank discrete devices with one 8Gb die each to the i.MX. 8DXL supports only one chip select for DDR3L therefore, dual-rank systems are not supported.

Note 9:

For single channel (x16) memory devices, the currently maximum available density in the market is 16Gb/2GB (6 Oct 2021).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sir or Madam,

Thank your for your information.

It seems to have confirmed that 2*4GB is in use. How about 1*8GB?

Due to 1*8GB has the advantage of using space, is there any information about using 1*8GB here?

Or is it not recommended to use LPDDR*1 design architecture here?

I am looking forward to your reply.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

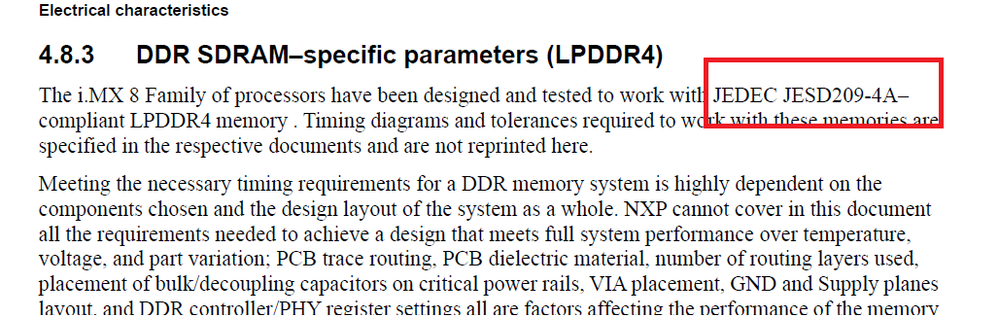

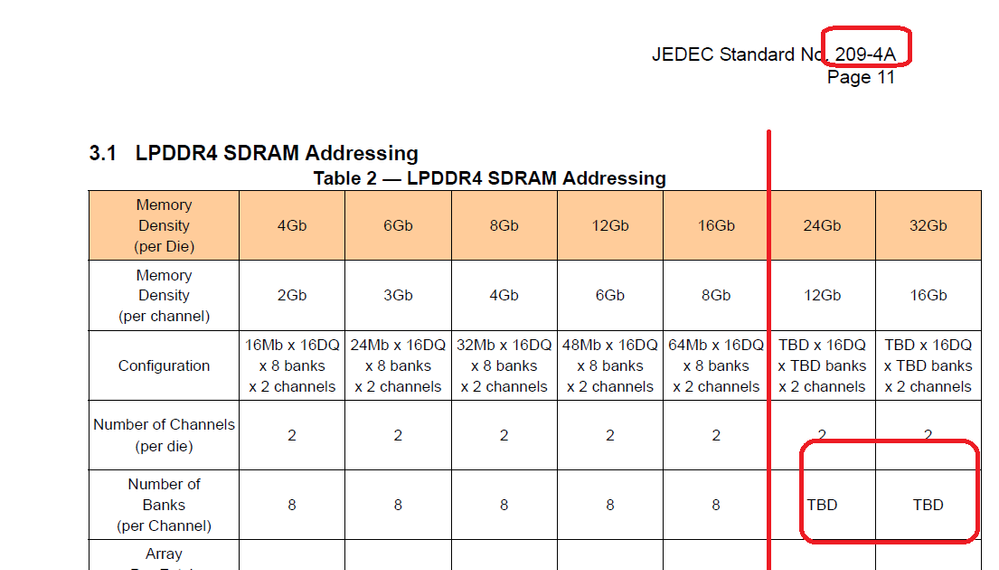

In the i.MX8QM datasheet, it already told you JESD209-4A not JESD209-4B.

It is very solid information.

Memory Density (per channel) is 8Gb. "b" not "B" in JESD209-4A.

If you check your question again, you will find your question has no enough information. number of cs? number of ddr phy? channel?

the configuration should be like 64Mb x 16DQ x 8 banks x 2 channels. Not 4GBx2, 8GBx1. that is cs, not configuration.

and if you read the ddr part datasheet, it is exactly the same as JEDEC spec. i.MX and ddr part, they all follow the spec.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry we do not have that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is a list of maximum supported LPDDR4 memory on the i.MX 8QM / 8X / 8XL:

| SoC | Package | Max data bus width | Maximum density | Assumed memory organization | Notes |

| i.MX 8QM/8QP | 29x29 mm | 32-bit (per controller) | 32Gb/4GB (per controller) | dual rank, dual-channel device with 16-row addresses (R0-R15) | 1, 2, 4 |

| i.MX 8QXP/8DXP | 21x21 mm | 32-bit | 32Gb/4GB | dual rank, dual-channel device with 16-row addresses (R0-R15) | 1, 2, 4 |

| i.MX 8QXP/8DXP | 17x17 mm | 16-bit | 16Gb/2GB | dual rank, single-channel device with 16-row addresses (R0-R15) | 1, 2, 3, 4, 9 |

| i.MX 8DX | 21x21 mm | 16-bit | 16Gb/2GB | dual rank, single channel device with 16-row addresses (R0-R15) | 1, 2, 3, 4, 9 |

| i.MX 8DX | 17x17 mm | 16-bit | 16Gb/2GB | dual rank, single channel device with 16-row addresses (R0-R15) | 1, 2, 3, 4, 9 |

| i.MX 8DXL/8SXL | 15x15 mm | 16-bit | 32Gb/4GB | dual rank, single channel device with 17-row addresses (R0-R16) | 1, 2, 3, 9 |

Note 1:

The numbers are based purely on the IP vendor documentation for the DDR Controller and the DDR PHY, on the settings of the implementation parameters chosen for their integration into the SoC, and on the JEDEC standard JESD209-4A. Therefore, they are not backed by validation, unless said otherwise and there is no guarantee that apart with the specific density and/or desired internal organization is offered by the memory vendors. Should the customers choose to use the maximum density and assume it in the intended use case, they do it at their own risk.

Note 2:

Byte-mode LPDDR4 devices (x16 channel internally split between two dies, x8 each) of any density are not supported therefore, the numbers are applicable only to devices with x16 internal organization (referred to as "standard" in the JEDEC specification).

Note 3:

The memory vendors often do not offer so many variants of the single-channel memory devices. As an alternative, a dual-channel device with only one channel connected may be used. For example:

A dual-rank, single-channel device with 16-row address bits has a density of 16Gb. If such a device is not available at the chosen supplier, a dual-rank, dual-channel device with 16-row address bits can be used instead. This device has a density of 32 Gb however since only one channel can be connected to the SoC, only half of the density is available (16 Gb).

Usage of more than one discrete memory chip to overcome market constraints is not supported since only point-to-point connections are assumed for LPDDR4.

Note 4:

Devices with 17-row addresses (R0-R16) are not supported by the SoCs.

Note 5:

The numbers are based purely on the IP vendor documentation for the DDR Controller and the DDR PHY, on the settings of the implementation parameters chosen for their integration into the SoC and on the JEDEC standard JESD79-3E/JESD79-3F Therefore, they are not backed by validation, unless said otherwise and there is no guarantee that a part with the specific density and/or desired internal organization is offered by the memory vendors. Should the customers choose to use the maximum density and assume it in the intended use case, they do it at their own risk.

Note 6:

The density can be achieved by connecting 8 single rank discrete devices with one 8Gb die each, 4 devices connected to each chip select or by connecting 4 dual rank discrete devices with two 8Gb dies each. Note that this number of discrete devices significantly exceeds the number of devices used on the validation board (2 discrete devices, not taking into account the device used for ECC) therefore, it is not guaranteed that the i.MX would be able to drive the signals with margin to the required voltage levels due to increased loading on the traces. Significant effort would be required in terms of PCB layout and signal integrity analysis. Practically, it is not recommended to use more than 2 discrete DDR3L devices. This corresponds to the maximum density of 16Gb/2GB in case of the single rank devices containing one 8Gb die or 32Gb/4GB in case of the dual-rank devices containing two 8Gb dies (x16 8Gb devices with 16-row addresses and 10 column addresses assumed instead of x8 devices in such case).

Note 7:

The density can be achieved by connecting 4 single rank discrete devices with one 8Gb die each, 2 devices connected to each chip select or by connecting 2 dual rank discrete devices with two 8Gb dies each. Note that the first option exceeds the number of devices used on the validation board (2 discrete devices) therefore, it is not guaranteed that the i.MX would be able to drive the signals with margin to the required voltage levels due to increased loading on the traces. Significant effort would be required in terms of PCB layout and signal integrity analysis. Practically, it is not recommended to use more than 2 discrete DDR3L devices. This corresponds to the maximum density of 16Gb/2GB in case of the single rank devices containing one 8Gb die or 32Gb/4GB in case of the dual-rank devices containing two 8Gb dies.

Note 8:

The density can be achieved by connecting 2 single rank discrete devices with one 8Gb die each to the i.MX. 8DXL supports only one chip select for DDR3L therefore, dual-rank systems are not supported.

Note 9:

For single channel (x16) memory devices, the currently maximum available density in the market is 16Gb/2GB (6 Oct 2021).