- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

In Imx6 Quad , after pressing RESET switch SOM doesn't boot again. it boots only after hard power on/off.

As per my understanding, through external reset released, internal Reset will release only after VDD_ARM_CAP and VDD_SOC_CAP supplies

are stable (internal LDO_CORE and LDO_SOC).

so , i doubt these internal voltage domains and their input voltages VCC_SW1AB_CORE and VCC_SW1C_SOC of PMIC (MMPF0100F0AEP)

Findings:

1. in Linux, boots after reset switch is pressed with out problem and VCC_SW1AB_CORE and VCC_SW1C_SOC voltages of PMIC are fine. ( no voltage dip occurs-here current consumption from VCC_SW1AB_CORE is < 500mA)

2. In android

1. if reset switch is pressed at the time of uboot, and kernel loading , booting occurs without problem ( up to this process current consumption form VCC_SW1AB_CORE is < 700mA )

2. once android application launches , current consumption from VCC_SW1AB_CORE is increased >900mA, and voltages dip occurs ( snap shot attached) if reset switch is pressed now, doesn't boot again.

3. first dip occurs from 1.35 to 1.28V at that time current is around 700mA. if i press reset switch here, boot occurs without problem

4. After some time ( launching android application) continuous dip occurs from ( 1.28V to 0.992V) here current is around 900mA . if i reset here, board doesn't boot . and VCC_SW1AB_CORE is in 0.992V itself.

Green -VCC_SW1AB_CORE of PMIC

Blue- VCC_SW1C_SOC of PMIC

Same issues occurs in 3 boards.

Is anyone faced this issue...? Pls let me know the solution for this.?

Thanks

Tamilarasan.

已解决! 转到解答。

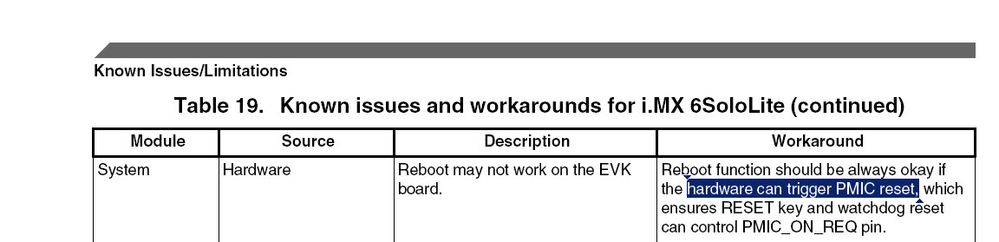

HI Tamilarasan

recommended to use such reset circuit , which resets both PMIC and

i.MX6, because for example, if i.MX6 in ldo-bypas mode, resetting only

processor will hang it (PMIC voltages may be insufficient for successful boot).

This is addressed by Sabre SD reset circuit design (WDOG connection to PWRON)

i.MX6_SABRE_SDP_DESIGNFILES spf-27392 p.21 and description in Release Notes

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

HI Tamilarasan

recommended to use such reset circuit , which resets both PMIC and

i.MX6, because for example, if i.MX6 in ldo-bypas mode, resetting only

processor will hang it (PMIC voltages may be insufficient for successful boot).

This is addressed by Sabre SD reset circuit design (WDOG connection to PWRON)

i.MX6_SABRE_SDP_DESIGNFILES spf-27392 p.21 and description in Release Notes

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------