- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- iMX6 Quad PoP Package supporting LPDDR2

iMX6 Quad PoP Package supporting LPDDR2

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

iMX6 Quad PoP Package supporting LPDDR2

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Reader,

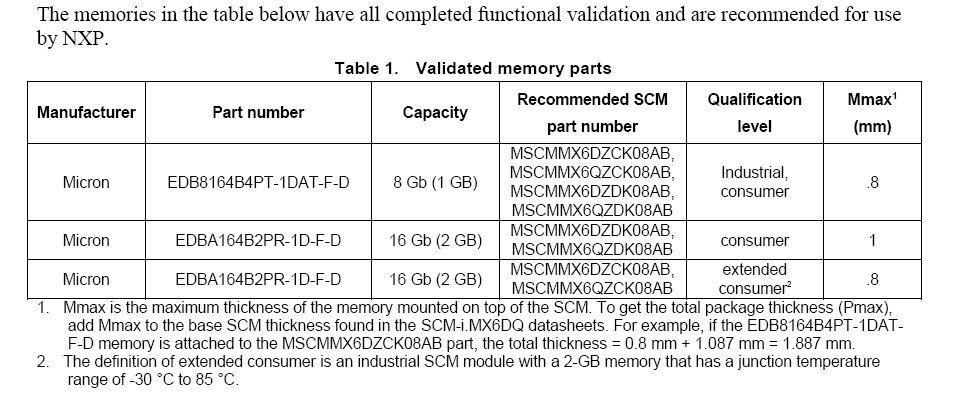

I want to use the PoP version of iMX6 in my new design. But there are no reference schematics for the same. Neither are any supported LPDDR2 memories described. I reference some of the blogs regarding the same in community and found that EDB8164B4PT-1DAT-F is compatible.

When I saw the pin connection between two I made following observation:

As per the ball assignment processor channel 1 is connected to memory die 0 and, processor channel 0 is connected to memory die 1. But he Clock Enable signal (CKE_Px) is exchanged, i.e. Processor CKE0_P0 is connected to Memory CKE_A and CKE0_P1 is connected to CKE_B.

Will this configuration work? Or is there any other LPDDR supported?

Thanks in advance.

Pranav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir,

Thanks for your kind reply. We are planning to use MCIMX6Q7CZK08AE in our system to get smallest form factor. Moreover MT42L128M64D2LL-25 is obsolete. So EDB8164B4PT-1DAT-F is replacement of the same. But still clock enable is crossed.

Please clarify.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

DRAM_CKE0P0 AA29 , DRAM_CKE1P0 Y29 in Table 85. 12 x 12 mm

Functional Contact Assignments i.MX 6Dual/6Quad Consumer-PoP

Applications Processor Data Sheet are defined per sect.2.1 LPDDR2 12x12 PoP 2-channel 2x32 package

ballout LPDDR2 JESD209-2D specification.

https://www.nxp.com/docs/en/data-sheet/IMX6DQCPOPEC.pdf

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pranav

one can look at below links (also some info were sent via mail)

https://community.nxp.com/thread/472137

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------