- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: iMX6 + KSZ9031: uboot dhcp after sw reset

iMX6 + KSZ9031: uboot dhcp after sw reset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX6 + KSZ9031: uboot dhcp after sw reset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there, we are using a board with an iMX6QP and a KSZ9031.

When we power the board we have 1GBps connection without a problem in both uboot and kernel.

The problem is that after a reboot, we cannot get ip address from dhcp in uboot.

If we boot from Nand, kernel can fix the mac/phy/dhcp issue.

Any ideas about what is happening? Thanks in advance for your help!

The u-boot log error is:

U-Boot 2017.03+g3cd63a0cef (Sep 06 2019 - 09:40:31 +0000)

CPU: Freescale i.MX6QP rev1.0 at 792MHz

CPU: Industrial temperature grade (-40C to 105C) at 39C

Reset cause: WDOG

DRAM: 1 GiB

NAND: 128 MiB

MMC: FSL_SDHC: 0

In: serial

Out: serial

Err: serial

Net: FEC [PRIME]

Autoboot in 2 seconds

=> dhcp

BOOTP broadcast 1

BOOTP broadcast 2

BOOTP broadcast 3

BOOTP broadcast 4

BOOTP broadcast 5

BOOTP broadcast 6

BOOTP broadcast 7

BOOTP broadcast 8

BOOTP broadcast 9

The uboot code is:

/* rgmi enet */

static iomux_v3_cfg_t const enet_pads[] = {

MX6_PAD_ENET_MDIO__ENET_MDIO | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_MDC__ENET_MDC | MUX_PAD_CTRL(ENET_PAD_CTRL),MX6_PAD_RGMII_TXC__RGMII_TXC | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_TX_CTL__RGMII_TX_CTL | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_TD0__RGMII_TD0 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_TD1__RGMII_TD1 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_TD2__RGMII_TD2 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_TD3__RGMII_TD3 | MUX_PAD_CTRL(ENET_PAD_CTRL),MX6_PAD_RGMII_RXC__RGMII_RXC | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_RX_CTL__RGMII_RX_CTL | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_RD0__RGMII_RD0 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_RD1__RGMII_RD1 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_RD2__RGMII_RD2 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_RGMII_RD3__RGMII_RD3 | MUX_PAD_CTRL(ENET_PAD_CTRL),MX6_PAD_ENET_REF_CLK__ENET_TX_CLK | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_CRS_DV__GPIO1_IO25 | MUX_PAD_CTRL(ENET_PAD_CTRL), /*int*/

MX6_PAD_ENET_TX_EN__GPIO1_IO28 | MUX_PAD_CTRL(ENET_PAD_CTRL), /*rst*/

};static int reset_enet_phy()

{

/* Reset KSZ9031 PHY */

gpio_request(GPIO_ETH_RESET, "GPIO_ETH_RESET");gpio_direction_output(GPIO_ETH_RESET, 0);

mdelay(10);

gpio_set_value(GPIO_ETH_RESET, 1);

mdelay(100);gpio_free(GPIO_ETH_RESET);

return 0;

}int board_phy_config(struct phy_device *phydev)

{

/* Joan: errata 5: Autonegotiation link-up failure due FLP interval */

ksz9031_phy_extended_write(phydev, 0x0, 0x3, MII_KSZ9031_MOD_DATA_NO_POST_INC, 0x1A80);

ksz9031_phy_extended_write(phydev, 0x0, 0x4, MII_KSZ9031_MOD_DATA_NO_POST_INC, 0x0006);///tret de udoo, apalis no ho te: ho deixo per defecte

phy_write(phydev, MDIO_DEVAD_NONE, MII_CTRL1000, 0x1c00);/* control data pad skew - devaddr = 0x02, register = 0x04 */

ksz9031_phy_extended_write(phydev, 0x02,

MII_KSZ9031_EXT_RGMII_CTRL_SIG_SKEW,

MII_KSZ9031_MOD_DATA_NO_POST_INC, 0);

/* rx data pad skew - devaddr = 0x02, register = 0x05 */

ksz9031_phy_extended_write(phydev, 0x02,

MII_KSZ9031_EXT_RGMII_RX_DATA_SKEW,

MII_KSZ9031_MOD_DATA_NO_POST_INC, 0);

/* tx data pad skew - devaddr = 0x02, register = 0x06 */

/*ksz9031_phy_extended_write(phydev, 0x02,

MII_KSZ9031_EXT_RGMII_TX_DATA_SKEW,

MII_KSZ9031_MOD_DATA_NO_POST_INC, 0);*/

/* gtx and rx clock pad skew - devaddr = 0x02, register = 0x08 */

ksz9031_phy_extended_write(phydev, 0x02,

MII_KSZ9031_EXT_RGMII_CLOCK_SKEW,

MII_KSZ9031_MOD_DATA_NO_POST_INC, 0x03FF);if (phydev->drv->config)

phydev->drv->config(phydev);return 0;

}int board_eth_init(bd_t *bis)

{imx_iomux_v3_setup_multiple_pads(enet_pads, ARRAY_SIZE(enet_pads));

reset_enet_phy();

return cpu_eth_init(bis);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi joan

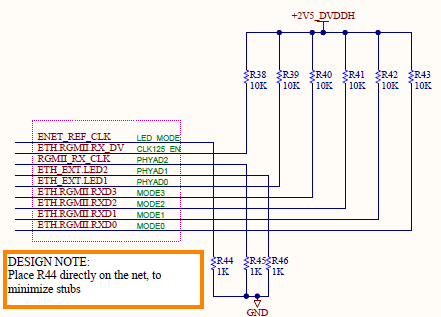

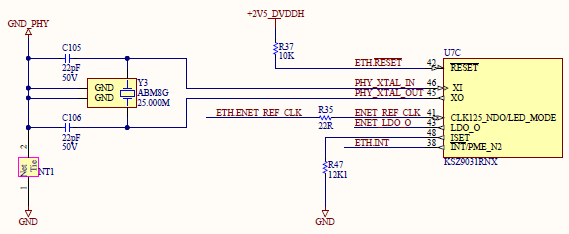

one can check if KSZ9031 was correctly reset and its power-up sequence

according to its datasheet. In general such issues may happen when reboot

performing without full board reset as it is done in NXP i.MX6QP Sabre SD

reference board (p.21 U507, with WDOG_B and PWRON SPF-28857.pdf schematic)

Design files, including hardware schematics, Gerbers, and OrCAD files for i.MX 6QuadPlus (i.MX 6Dual...

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------