- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX8M mini MSCALE_DDR_Tool - LPDDR4 Stress Test fails

i.MX8M mini MSCALE_DDR_Tool - LPDDR4 Stress Test fails

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX8M mini MSCALE_DDR_Tool - LPDDR4 Stress Test fails

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Everyone,

I made a design with i.MX8M mini (MIMX8MM6DVTLZAA) and LPDDR4 (MT53B512M32D2DS-062 AIT:C).

The schematic and the Layout are the same as on the EVK but we use another PMIC.

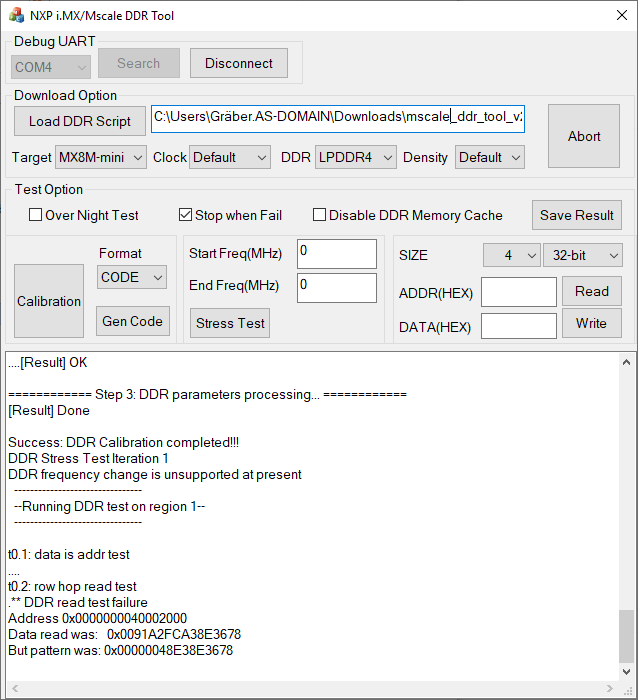

Now I'm trying to perform a stress test with MSCALE_DDR_Tool.

The calibration seems to work. I get "Success: DDR Calibration completed!!!" but wenn I start the stress test t0.2 fails:

If I perform a manual Write/Read to that address, it works.

I tried to reduce the Clock Cycle Frequency to 800 MHz but then calibration fails with different messages:

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @800Mhz...

Failed to find sufficient CA Vref Passing Region for CS 0 channel 0

PMU: ***** Assertion Error - terminating *****

[Result] FAILED

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @800Mhz...

[Process] End of CA training

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of read DQ deskew training

PMU: Error: Dbyte 0 nibble 0 rxClkDly passing region is too small (width = 0)

PMU: ***** Assertion Error - terminating *****

[Result] FAILED

Any ideas?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please check carefully if board meets requirements of Hardware Development Guide for the i.MX8Mm,

in particular - DRAM routing recommendations.

https://www.nxp.com/docs/en/user-guide/IMX8MMHDG.pdf

Have a great day,

Yuri

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

we copied the EVK schematic and Layout so we should actually meet all requirements of the HWDG.

If there are any design problems in the layout, the LPDDR4 should work with lower speed.

How can I perform a test with 800MHz? What does the mentioned ERROR message mean?

I changed "Clock Cycle Freq (MHz)" to 800MHz in the Excel File "MX8M_Mini_LPDDR4_RPA_v11.xlsx" and modified the "TBD" field in the .ds file

"memory set 0x30360054 32 0x0012C09"

Do I have to adjust any other values to run the LPDDR4 with 800MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, I found the problem.

MT53B512M32D2DS-062 AIT:C Dual-Channel, Dual-Rank

MT53D512M32D2DS-053 WT:D Dual-Channel, Single-Rank