- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX8M Nano LPDDR4 Calibration failed - CA Training Failed

i.MX8M Nano LPDDR4 Calibration failed - CA Training Failed

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX8M Nano LPDDR4 Calibration failed - CA Training Failed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have designed custom board with i.MX8M Nano CPU and wiring mainly based on your Evaluation board, but when I try to calibrate DDR with DDR Tool, then I get "PMU: Error: CA Training Failed.". I have no idea what is wrong. I tried different configurations in RPA excel file, but nothing helped.

Additionally, after pushing ".ds" file to the board, on the beginning I get this message:

"I2C_I2SR(0x30a2000c):0x93

bus is not ready"

Here you have full output:

Download is complete

Waiting for the target board boot...

I2C_I2SR(0x30a2000c):0x93

bus is not ready

hardware_init exit

*************************************************************************

*************************************************************************

*************************************************************************

MX8 DDR Stress Test V3.10

Built on Feb 5 2020 13:02:45

*************************************************************************

--Set up the MMU and enable I and D cache--

- This is the Cortex-A53 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug

- VMCR Check:

- ttbr0_el3: 0x97d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x1122

- MMU and cache setup complete

*************************************************************************

ARM clock(CA53) rate: 1500MHz

DDR Clock: 1600MHz

============================================

DDR configuration

DDR type is LPDDR4

Data width: 16, bank num: 8

Row size: 16, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 1

Density per chip select: 1024MB

Density per controller is: 1024MB

Total density detected on the board is: 1024MB

============================================

MX8M-nano: Cortex-A53 is found

*************************************************************************

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @1600Mhz...

PMU: Error: CA Training Failed.

PMU: ***** Assertion Error - terminating *****

[Result] FAILED

My DDR is Kingston D0811PM1WDGTK-U 1GB version. I have attached RAM datasheet and my RPA config file.

I don't know if this is important, but on my board, Voltage converter is connected to i2c4 instead i2c1 like it was on your Eval board. Is this possible that DDR Tool can not calibrate RAM because program is trying to use converter on i2c1 instead of i2c4 ?

I would be really thankful for helping me find the source of the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

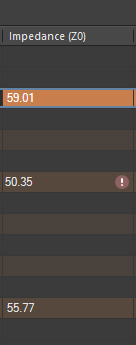

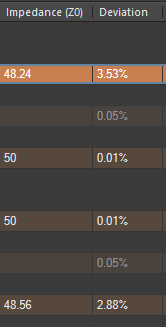

If target impedance is missing, reduce clock frequency for RAM should allow to start work with device?

Somewhere there was a calculation mistake and it's between 50 and 60 Ohm...

About signal strenght, you mean register DDRC_INIT4 and value for EMR2 ? (Pull-Down Drive Strength)

Best regards

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adrian

>If target impedance is missing, reduce clock frequency for RAM should allow to start work with device?

I doubt if this could help, as memories signal quality may be not good.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MatiPL

>Voltage converter is connected to i2c4 instead i2c1 like it was on your Eval board.

>Is this possible that DDR Tool can not calibrate RAM because program is trying

>to use converter on i2c1 instead of i2c4 ?

yes this may be the reason. One can try to tweak it using below examples:

"Sample configuration in the front of the .ds script for i.MX8MM PMIC configuration"

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have added PMIC config section to ".ds" file, changed i2C bus index and IOMUXC registers, and additionally removed "pmic_set" lines (sample configuration applies to another PMIC model so doesn't fit my PMIC). Now instead "bus is not ready" I get "PMIC is initialized in DDR script", but unfortunately I still have "PMU: Error: CA Training Failed." when I try run calibration.

My PMIC is PCA9450B and I am not sure, but I guess for LPDDR4 this PMIC doesn't need any "pmic_set" instructions to work properly with this memory type. Or maybe I am wrong and should add something more to the PMIC config section ?

Now this section looks like this:

##############step 0.5: configure I2C port IO pads according to your PCB design. #####

########### You can modify the following instructions to adapt to your board PMIC #######

memory set 0x3033022c 32 0x00000010 #IOMUXC_SW_MUX_I2C4_SCL

memory set 0x30330230 32 0x00000010 #IOMUXC_SW_MUX_I2C4_SDA

memory set 0x30330494 32 0x000000C6 #IOMUXC_SW_PAD_I2C4_SCL

memory set 0x30330498 32 0x000000C6 #IOMUXC_SW_PAD_I2C4_SDA

sysparam set pmic_cfg 0x034B #bit[7:0] = PMIC addr,bit[15:8]=I2C Bus Bus index from 0 ('0' = I2C1, '1' = I2C2, '2' = I2C3, '3' = I2C4)

Thanks for helping,

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MatiPL

"PMU: Error: CA Training Failed." may be due to signal timings or integrity

issues, one can try to tweak signals driver strength (search in RPA tool "strength")

and recheck memory layout using

i.MX 8QuadMax/i.MX 8QuadXPlus Hardware Developer’s Guide

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

We redesign layout and now should be better:

But still the memory calibration fails.

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @1000Mhz...

PMU: Error: CA Training Failed.

PMU: ***** Assertion Error - terminating *****

[Result] FAILED

I tried 1600MHz, 1000MHz and 800MHz of DDR with no success.

Registers (DDRC_INIT4, DDRC_FREQ1_INIT4 and DDRC_FREQ2_INIT4) of Pull-Down Drive Strength we set at 2 (RZQ/2) (are there any recommendations to not set a strong signal or only EMC issue? )

All lines have 175ps latency including internal daley from Hardware Developer’s Guide.

Maybe something else is causing this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

could you try latest version MX8M_Nano_LPDDR4_RPA_v3.xlsx from link:

and mscale_ddr_tool_v310_setup.exe.zip :

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

If target impedance is missing, reduce clock frequency for RAM should allow to start work with device?

Somewhere there was a calculation mistake and it's between 50 and 60 Ohm...

About signal strenght, you mean register DDRC_INIT4 and value for EMR2 ? (Pull-Down Drive Strength)

Best regards

Adrian