- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX6 ONOFF Pull-up?

i.MX6 ONOFF Pull-up?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX6 ONOFF Pull-up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a question concerning the ONOFF pin using the iMX6 device. According to the data sheet, there should be an internal pull-up on this pin to VSNVS. However, we’re seeing that even when VSNVS is present the ONOFF pin is not being pulled up. Do you know if there really is an internal pull-up or if an external one needs to be applied?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to section 10.5 [ONOFF (Button)] of the i.MX6 DQ RM, the ONOFF signal,

asserted greater than 5 seconds, initiates a hardware-enforced power down request

to the power IC, assuming ONOFF is i.MX6 RESET_IN_B and the power IC is connected

the i.MX6 output PMIC_ON_REQ. The i.MX6 must have TEST_MODE LOW (free).

ONOFF (RESET_IN) signal has internal (100 KOhm ) pull-up, so can be left floating.

But under noisy environment – if internal 100 KOHm pull up is not strong enough – an external

resistor (of 10 KOhm) may be applied.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

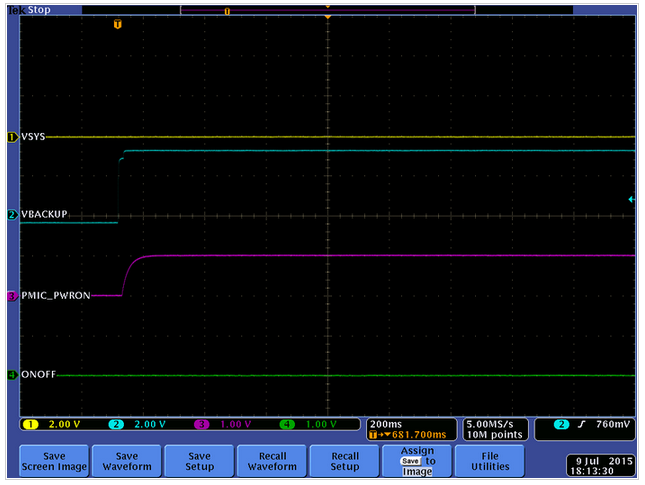

I’ve included some feedback from the customer that we’ve observed. Note that VSYS is the main input voltage to the PMIC and VBACKUP is the battery backup input to the PMIC:

In the first trace, when PMIC VBACKUP = 3.3V is applied, causing VSNVS to go to 1.0V, ONOFF does not pull up to 1.0V. It is only later (second trace) when 3.9V is applied to VSYS (PMIC VIN), resulting in VSNVS rising to 3.0V, that the PMIC beings the power on sequencing and ONOFF pulls up to VSNVS = 3.0V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Details of internal schematic implementation of i.MX6 pins are not provided.

(Some general scheme may be found at Figure 6 (Simplified internal structure

of the IOMUX for each pin) of app note AN5078 “Influence of Pin Setting on

System Function and Performance”

http://www.freescale.com/files/32bit/doc/app_note/AN5078.pdf

And when the i.MX6 environment is out of specified ranges (VSNVS < 2.8V)

its behavior is not guaranteed.

Regards,

Yuri.