- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX27 NAND BOOT ISSUE

i.MX27 NAND BOOT ISSUE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX27 NAND BOOT ISSUE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

I'm sorry for my poor English in advance.

I use the Chinese sent a related posts in the freescale community, because too few people reply, so the use of the English language.

My PCB is the second edition, the first edition is normal. Revised second edition just modified the interface to facilitate the extraction signal lines.

My board using serial download boot and kernel, then download the file system through the way of NFS.

I use ADSToolkit to download the boot and kernel that work work normally in the first edition, and prompts successfully downloaded, but the switch to boot from nand mode, the board can not start properly. Testing found the processor reads data from the nand, but DDR did not work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

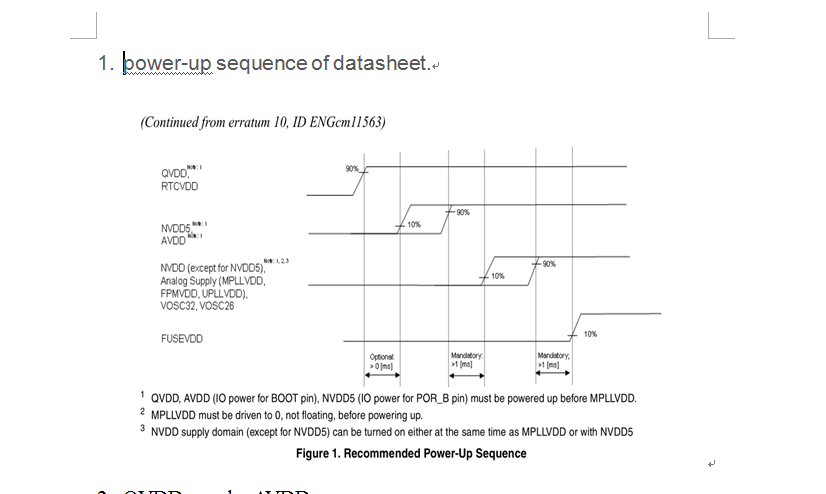

1.

Please check Your design regarding the recent i.MX27 Errata, if corresponding

workarounds are implemented.

< http://cache.freescale.com/files/32bit/doc/errata/MCIMX27CE.pdf >

In particular, please pay attention on ENGcm11563, ENGcm12387, ENGcm12388.

2.

You wrote, that DDR does not work. Is it possible to test memory ?

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello!

I passed the test found PLL did not work, no CLKO_PF15 400M processor output.

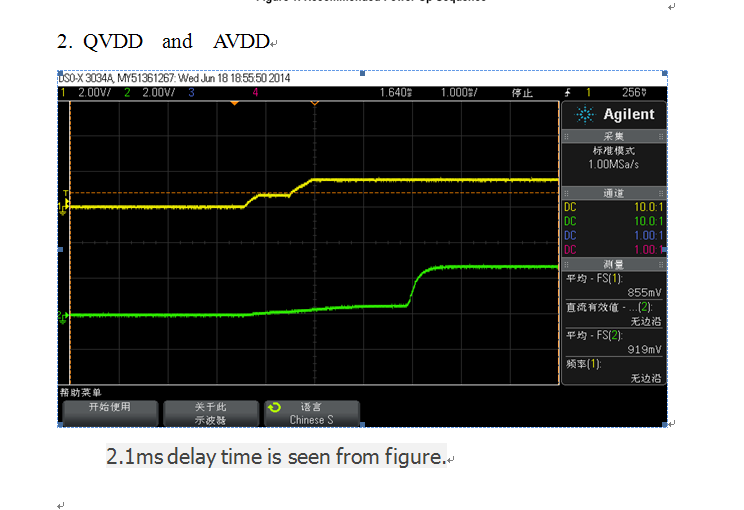

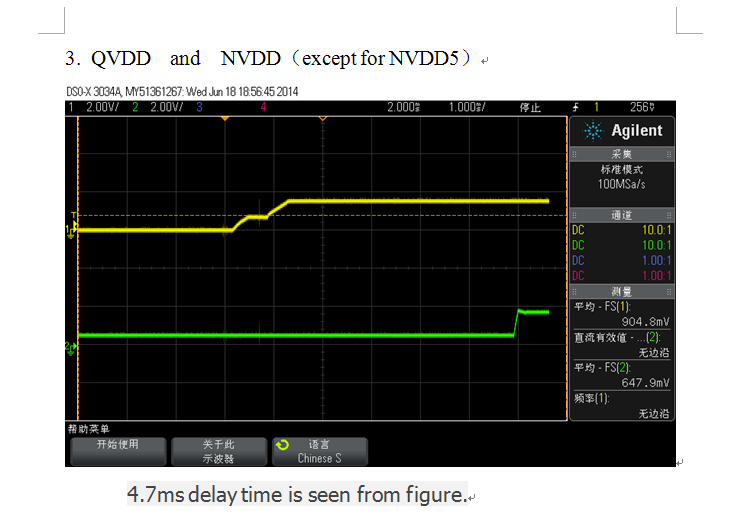

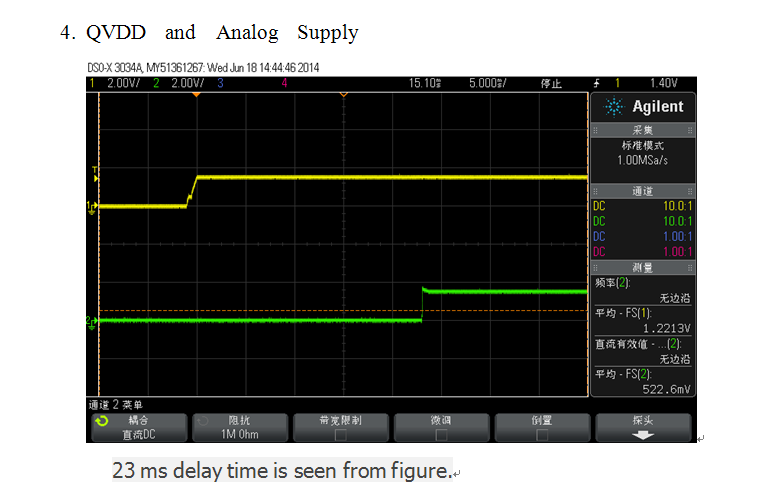

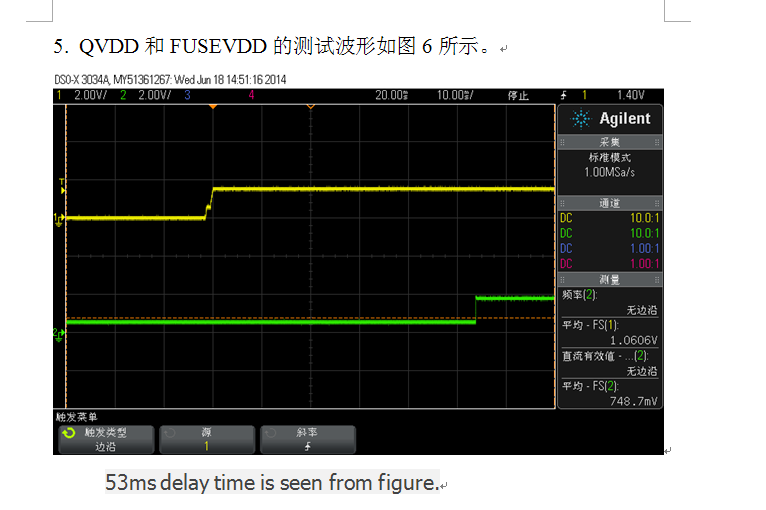

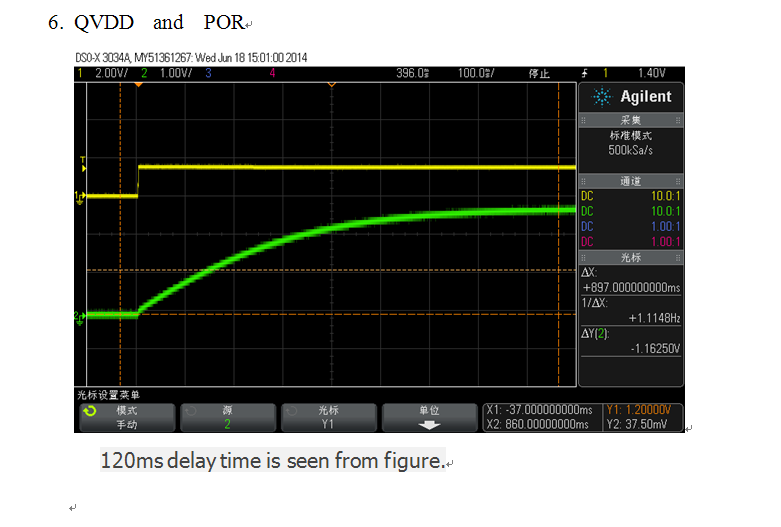

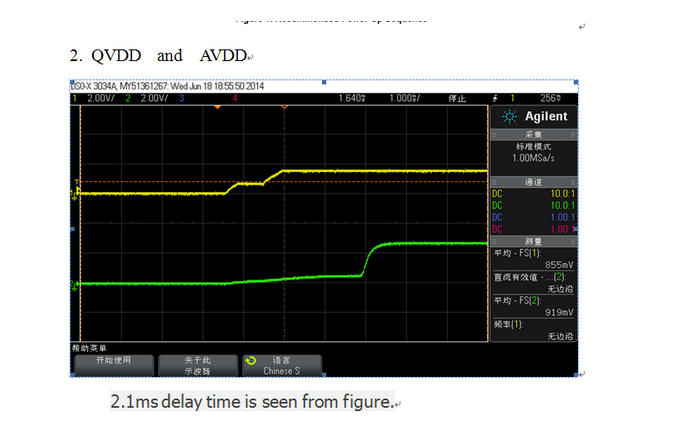

Our board power-up sequence is as follows。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

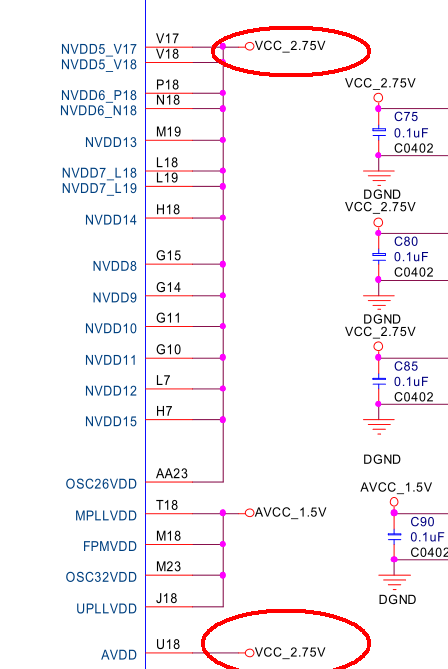

As for power up sequence, according to ENGcm11563 erratum :

NVCC5 must be powered up before MPLLVDD. On Your waveforms NVCC5 (NVDD5) is not present,

but from the schematic this requirement is not met.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Our power sequencing comply ENGcm11563 erratum requirements. NVDD_5 and AVDD are 2.75V supply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The power up sequence is correct.

But please pay attention on ENGcm12387, which takes place just for i.MX27 of new rev. 2.2.

Perhaps this is the reason why the first version of Your board was working, but new devices - do not.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Our first edition is working properly.

The processor is the same as the first edition.They are the same batch material.

What causes the PLL is not working properly?

And LPDDR the SI relationship?

In addition to power-up sequence, I can also check what hardware?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let me look at the schematic of system part (i.MX27, clocks, power, SDRAM, NAND)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The system can not upload files in PDF format. So I shot it.

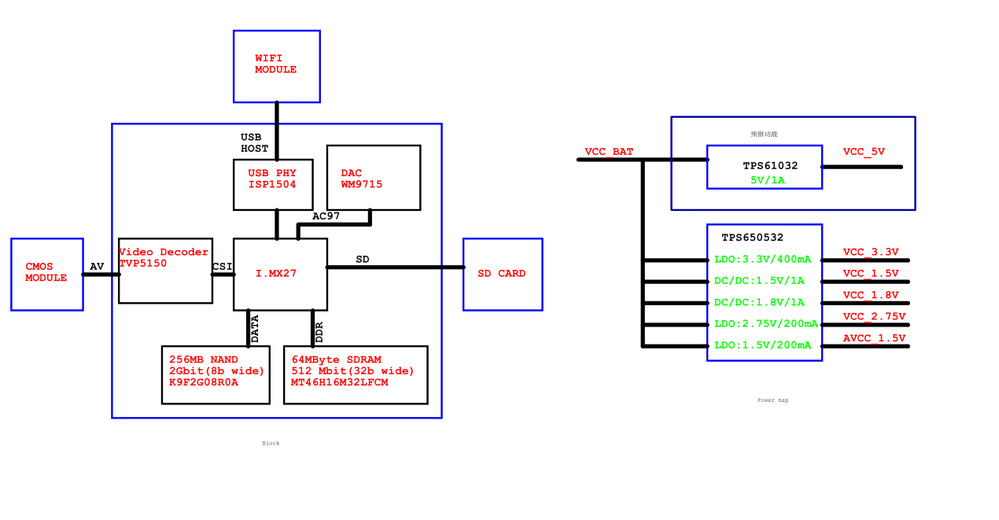

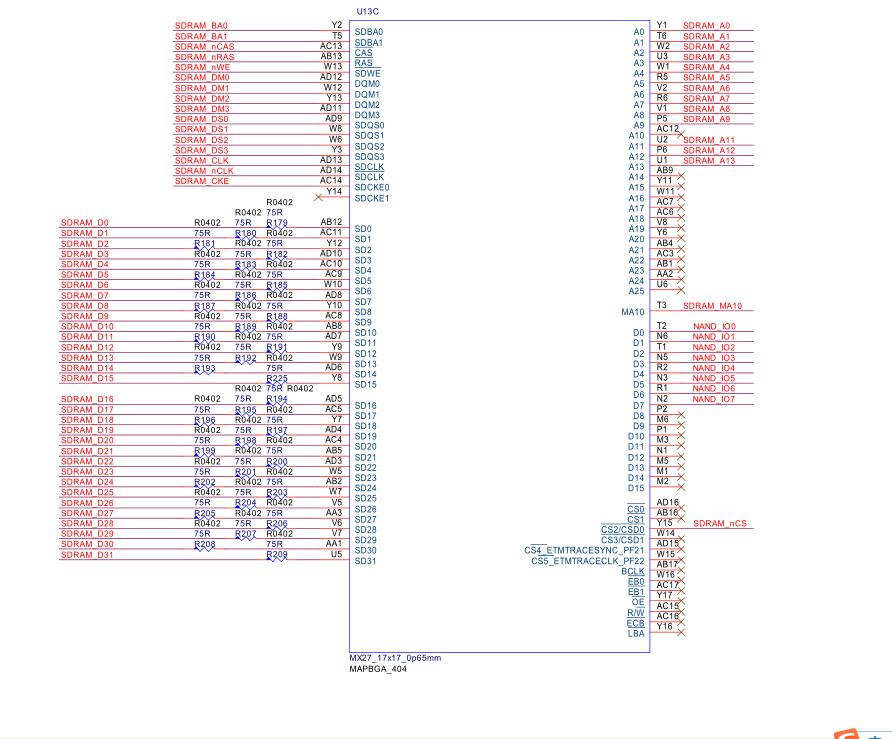

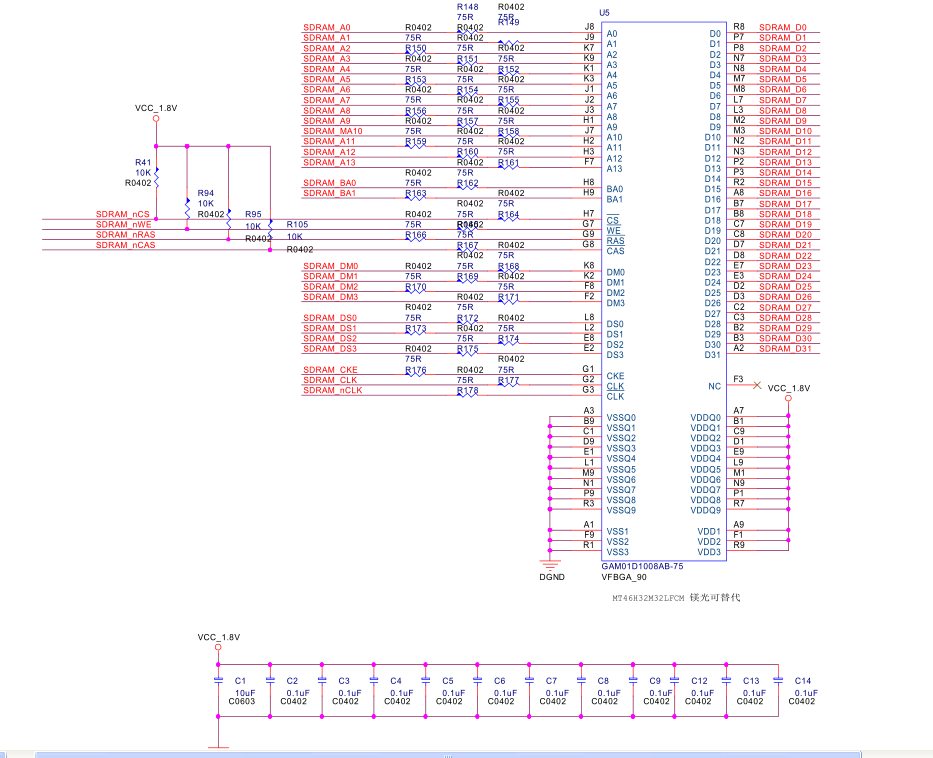

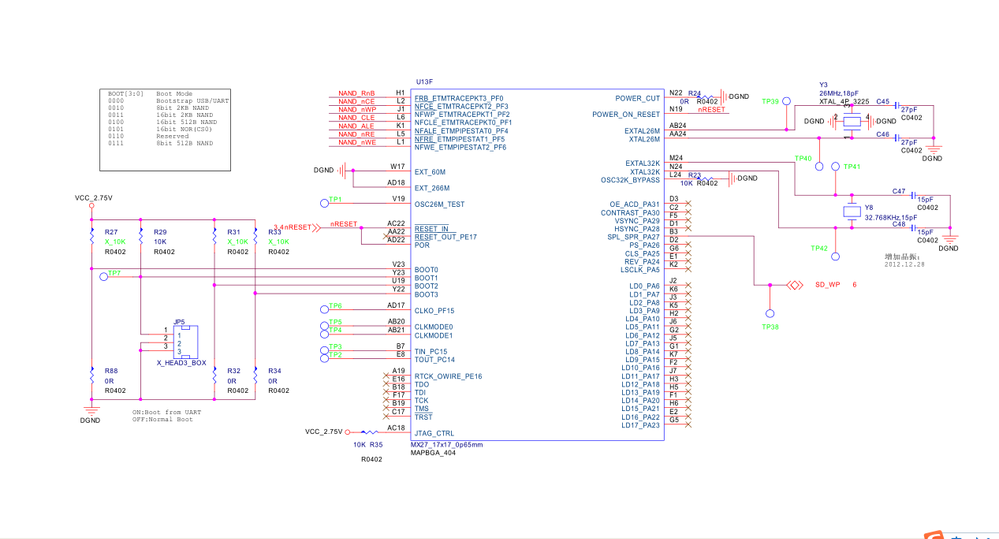

1. System block diagramSystem block diagram

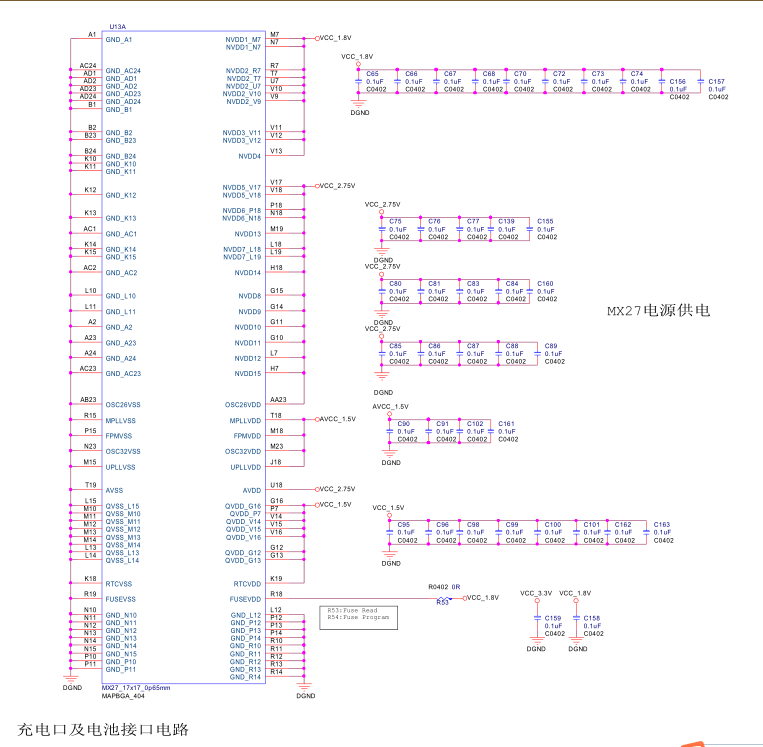

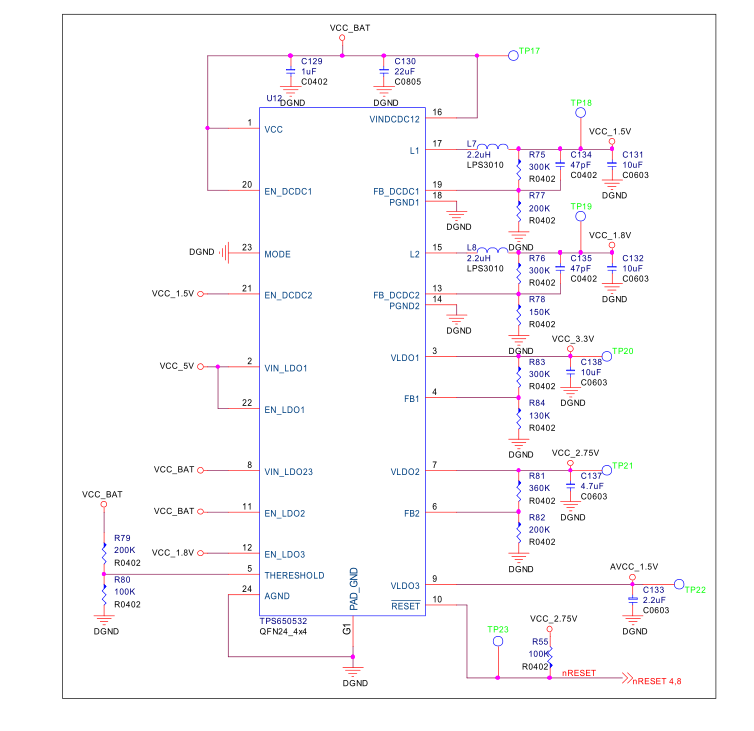

2. Power

The system can not upload files in PDF format. So I shot it.

Timing power on the board can not be modified.

power-on timing waveform before I use an external power supply to the board.

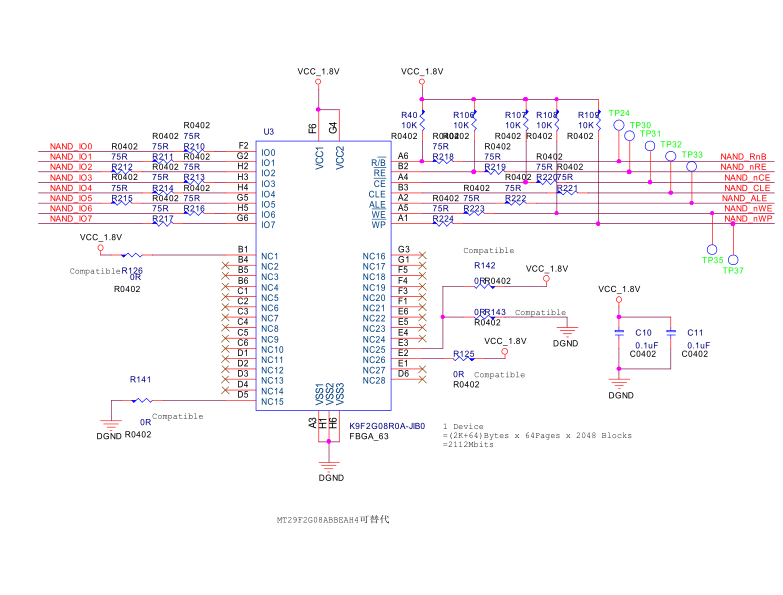

3. NAND and LPDDR

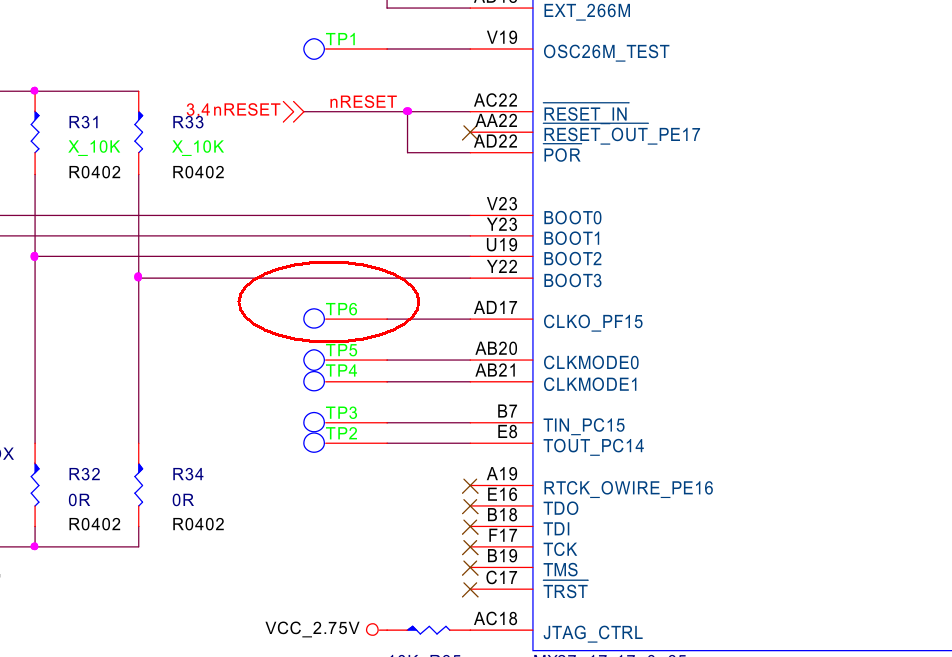

4. crystal and boot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1.

I do not see evident bugs on the scheme.

2.

You wrote about not working PLL - how it was detected ?

Note, by default the CLKO provides 32 KHz.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. When using the serial boot mode download boot, I can test to 32.768KHz square wave at the processor CLKO_PF15 pin .

2. I can test to 400M sine wave at the CLKO_PF15 pin from nand start in the first edition of the board, but test to high in the second edition of the board.

3. We blocked the following program in the bootloader, the processor can boot from NAND, but the frequency is wrong, the system is not working properly.

So I think the PLL is not working properly.

/* restart PLLs */

ldr r1, [r0, #(SOC_CRM_CSCR - SOC_CRM_BASE)]

orr r1, r1, #0x00080000

str r1, [r0, #(SOC_CRM_CSCR - SOC_CRM_BASE)]

SPLL_Not_Locked:

ldr r1, [r0, #(SOC_CRM_SPCTL1 - SOC_CRM_BASE)]

ands r1, r1, #0x8000

beq SPLL_Not_Locked

ldr r1, [r0, #(SOC_CRM_CSCR - SOC_CRM_BASE)]

orr r1, r1, #0x00040000

str r1, [r0, #(SOC_CRM_CSCR - SOC_CRM_BASE)]

MPLL_Not_Locked:

ldr r1, [r0, #(SOC_CRM_MPCTL1 - SOC_CRM_BASE)]

ands r1, r1, #0x8000

beq MPLL_Not_Locked /* reach here means MPLL is locked okay */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. There is data signal on the flash data signal line,but can not determine whether the read is complete.

In the serial boot mode, I use ADSToolkit tool to dump boot and kernel, and compare to the source file, no errors were found.

Can I give you a expression in Chinese?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> Can I give you a expression in Chinese?

OK, If Google helps :-)