- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: TP2850 de-interlace driver for iMX8MP boards

TP2850 de-interlace driver for iMX8MP boards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TP2850 de-interlace driver for iMX8MP boards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qiang_li-mpu_se and @joanxie ,

After referring to the website you provided, there will be a problem that mx8_v4l2_cap_drm_64 cannot be recorded, please help analyze this issue, thank you.

Here is my environment:

HW platform: IMX8MP

Video-In: TP2850

Linux Version: 5.10.52

Android Version: 11

Refer to your previous article on de-interlace:

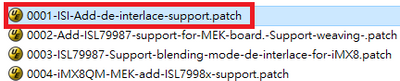

1. Refer to the Patch provided by your article (L5.4.0_2.3.0_ISL7998x_Patch.7z)

2. After unzip, I refer to 0001-ISI-Add-de-interlace-support.patch to Patch to my BSP

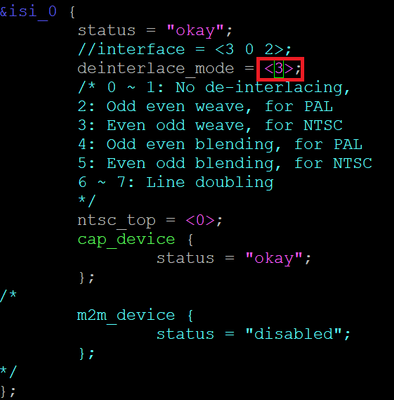

3. DTS isi_0 settings are as follows (NTSC weave mode):

4. After applying PATCH, use mx8_v4l2_cap_drm_64 to verify, the result cannot be recorded, it will always stop at (v4l2_device_streamon:1478): channel[0] v4l_dev=0x4 start capturing.

(command: mx8_v4l2_cap_drm_64 -cam 1 -d "/dev/video1" -fmt YUYV -ow 1280 -oh 720 –of)

5. The attached file is the LOG of the video recorded by mx8_v4l2_cap_drm_64, and the ISI0 register has been dumped.

Please help to analyze this issue, thank you.

Thanks

Fred

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you capture the stream to file and attach here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think you can check is there any other interrupt happens in ISI_CHNL_STS register.

And in isi_capture driver code, is there any code skip some frames. This is BSP version related.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qiang_li-mpu_se ,

As attached file LOG.

CHNL_STS is 0x100.

[ 64.904867][ T1793] mxc-isi 32e00000.isi: CHNL_STS[0x14]: 100

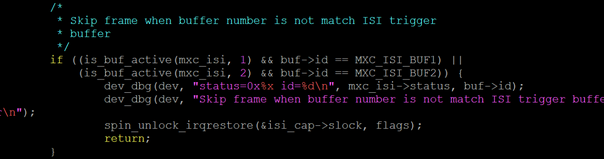

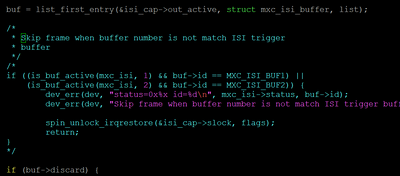

imx8-isi-cap.c: only skip frame once

[ 89.369850][ C0] isi-capture 32e00000.isi:cap_device: Skip frame when buffer number is not match ISI trigger buffer

Do you have any suggestions for DEBUG?

Thanks

Fred

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

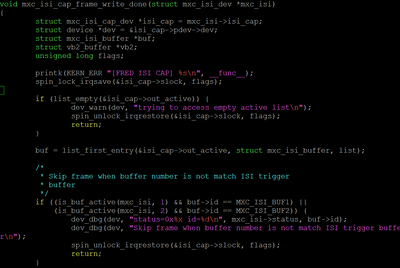

These codes should be removed, for de-interlace mode, each buffer will generate two interrupts, so it will not align with buffer buffer number.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qiang_li-mpu_se ,

I have removed these codes, but the output still does not improve.

Remove code: (imx8-isi-cap.c -> mxc_isi_cap_frame_write_done)

output:

Thanks

Fred

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

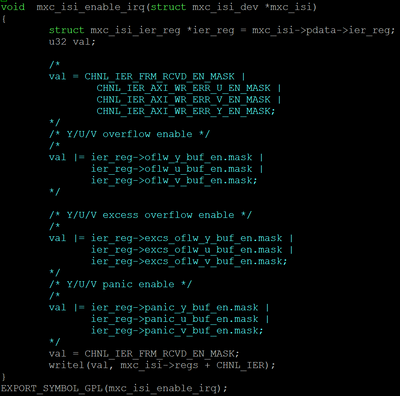

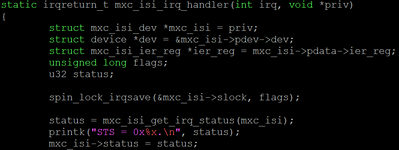

Please print out the CHNL_STS register value for each interrupt in function mxc_isi_irq_handler():

status = mxc_isi_get_irq_status(mxc_isi);

+ printk("STS = 0x%x.\n", status);

And in mxc_isi_enable_irq() function, you can just enable RCVD interrupt to try:

void mxc_isi_enable_irq(struct mxc_isi_dev *mxc_isi)

{

u32 val;

val = CHNL_IER_FRM_RCVD_EN_MASK;

writel(val, mxc_isi->regs + CHNL_IER);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qiang_li-mpu_se ,

The code has been modified as you suggested,

imx8-isi-hw.c

imx8-isi-core.c

Thanks

Fred

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Bit 17 EARLY_VSYNC_ERR appears in each interrupt, that means before ISI received 720 lines of video, VSYNC appears. So the TP2850 output field data is not 1280*720, you need identify the correct resolution for TP2850, and set it into ISI.

For example, if the TP2850's output is 720*240 field size, and you set 1280*720 in ISI, then you will get current issue, EARLY_VSYNC_ERR appears, and in capture buffer, there is only video data at the start of the buffers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qiang_li-mpu_se ,

The output of TP2850 is NTSC signal with a resolution of 720x480.

I modified camera_metadata(720X480), but the result is still the same, is there anything else that needs to be confirmed??

The attached file is the camera metadata and the test LOG after modifying the camera metadata.

Thanks

Fred

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From register "CHNL_IMG_CFG[0x0c]: 2d00500", it is still 1280*720.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qiang_li-mpu_se ,

I use the following command instead, setting the output to 720x480:

mx8_v4l2_cap_drm_64 -cam 1 -d "/dev/video1" -fmt YUYV -ow 720 -oh 480 -of

At this time, the CHNL_IMG_CFG register in the LOG is: 1e002d0 (720x480)

However, this setting will cause the screen to not be recorded. From the LOG, it can be found that it has been stuck in "start capturing".

Thanks

Fred