- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: TO: weidong Sun,基于Android 11移植WIFI_BT模组AW-CM276NF至i.MX 8MQ

TO: weidong Sun,基于Android 11移植WIFI_BT模组AW-CM276NF至i.MX 8MQ

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Weidong,

你好,我有一个关于WIFI/BT的问题想请教你。基于Android 11移植WIFI_BT模组AW-CM276NF至i.MX 8MQ。

1. 首先是硬件与官方开发板的区别

| 官方开发板imx8mq | 我们定制板 |

Wifi/BT模组 | AW-CM276MA-PUR | AW-CM276NF |

Android 11 PCIE接口 | Pcie2 | Pcie1 |

接口 | M2接口 | 直接焊接 |

2. 遇到的问题,在系统启动,初始化pcie的时候报如下错误:

[ 5.003183] imx6q-pcie 33800000.pcie: Phy link never came up

[ 5.009289] imx6q-pcie 33800000.pcie: failed to initialize host

[ 6.026260] imx6q-pcie 33800000.pcie: unable to add pcie port.

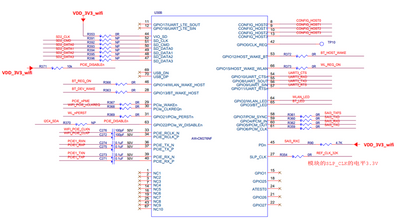

3. WIFI/BT部分的原理图如下

系统启动之后,GPIO的状态

- VDD_3V3_wifi: 3.3V电压正常

- PCIE_nPME:为高电平

- SAI3_RXC:为高电平

- WL_nPEREST:在上电过程中,有一个低电平拉低复位的操作

- CONFIG_HOST电平状态

CONFIG_HOST0: 1

CONFIG_HOST1: 1

CONFIG_HOST2: 0

- REF_CLK_32K:32.76K方波

- PCIE1_TXN/PCIE1_TXP: 高电平

- PCIE1_RXN/PCIE_RXP: 低电平

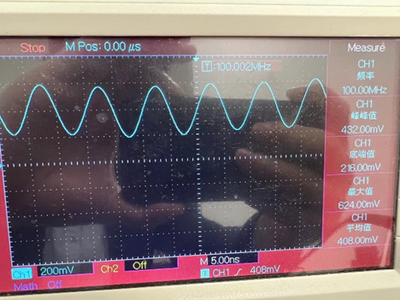

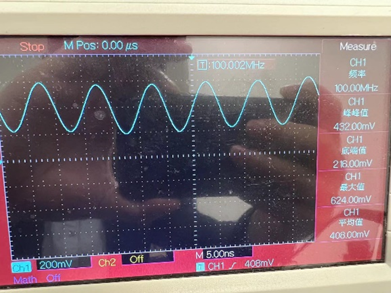

- WIFI_PCIE_CLKN/ WIFI_PCIE_CLKP波形如下:

4. 时钟发生器

PCIE1_REF_CLKP/PCIE1_REF_CLKN/WIFI_PCIE_CLKP/WIFI_PCIE_CLKN波形:

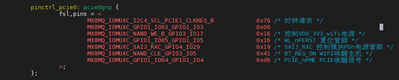

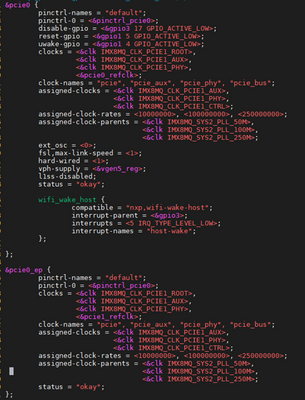

5. 软件设备树的配置:

6. 个人源码跟踪分析

我注意到日志中有报错“Phy link never came up”,而官方的开发板直接是“Link up”,日志对应的源码:"drivers/pci/controller/dwc/pcie-designware.c"

int dw_pcie_wait_for_link(struct dw_pcie *pci)

{

int retries;

/* Check if the link is up or not */

for (retries = 0; retries < LINK_WAIT_MAX_RETRIES; retries++) {

if (dw_pcie_link_up(pci)) {

dev_info(pci->dev, "Link up\n");

return 0;

}

usleep_range(LINK_WAIT_USLEEP_MIN, LINK_WAIT_USLEEP_MAX);

}

dev_info(pci->dev, "Phy link never came up\n");

return -ETIMEDOUT;

}

EXPORT_SYMBOL_GPL(dw_pcie_wait_for_link);

int dw_pcie_link_up(struct dw_pcie *pci)

{

u32 val;

if (pci->ops && pci->ops->link_up)

{

return pci->ops->link_up(pci);

}

val = readl(pci->dbi_base + PCIE_PORT_DEBUG1);

printk("@alan dw_pcie_link_up 2 val:[%x]\n", val);

return ((val & PCIE_PORT_DEBUG1_LINK_UP) &&

(!(val & PCIE_PORT_DEBUG1_LINK_IN_TRAINING)));

}

EXPORT_SYMBOL_GPL(dw_pcie_link_up);

由于pci->ops->link_up接口没有实例化,因此判断是否Link up 主要是读取寄存器readl(pci->dbi_base + PCIE_PORT_DEBUG1)。

经调试打印读取val的结果为0x 8200000,不满足Link up的条件。至于为什么读取的寄存器值不正确,我目前没有进一步跟踪的思路。

@weidong_sun 你能帮我分析一下“Phy link never came up”,出现的原因,以及相应的解决方法吗?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @pyh0603 ,

我从头开始看了一下你的描述。

1. Hardware

--PDn脚 拉高3.3V,OK

--CONFIG脚配置为PCIE UART接口,OK

--PERSTn和WDISABE拉高对的。

所以,hardware没啥问题。

2. software

我看到你的dts中,不仅添加了&pcie0节点,还加了pcie0-ep节点(这个不应该加,这是板子测试时,2个板子PCIE直接连接,一个做RC,一个做EP,进行传输速率测试用的)所以,你把pcie0-ep节点的status配置为disabled。

这样你的276模组应该可以工作了。

weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @pyh0603 ,

我从头开始看了一下你的描述。

1. Hardware

--PDn脚 拉高3.3V,OK

--CONFIG脚配置为PCIE UART接口,OK

--PERSTn和WDISABE拉高对的。

所以,hardware没啥问题。

2. software

我看到你的dts中,不仅添加了&pcie0节点,还加了pcie0-ep节点(这个不应该加,这是板子测试时,2个板子PCIE直接连接,一个做RC,一个做EP,进行传输速率测试用的)所以,你把pcie0-ep节点的status配置为disabled。

这样你的276模组应该可以工作了。

weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content