- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Need support for SAI_RX2 issue

Need support for SAI_RX2 issue

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Need support for SAI_RX2 issue

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP support,

IMX is the master, and the tuner is slave.

If we monitor the connection, we can see that the signal is squeeze to 0 and almost 0V (see attached picture)

We have done the test of connecting the tuner to SAI1_RX0 (instead of SAI1_RX2) and it we did get the correct signal/data.

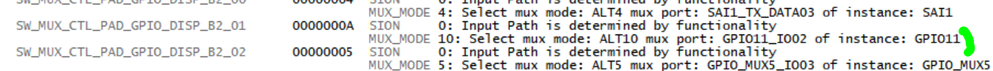

That means the issue is on the IMX side, we think this can be a pin config issue as the DISP_B2_01 is SAI1_RX2 and SAI1_TX2 but we don't know how to force RX mode.

Here some SAI1 registry dump during transfers

tcr1: 0x10 tcr2: 0x7000007 tcr3: 0x10000 tcr4: 0x10010f3b tcr5: 0xf0f0f00

rcr1: 0x10 rcr2: 0x47000007 rcr3: 0x40000 rcr4: 0x10010f1b rcr5: 0xf0f0f00

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

But what is the value of R4261? it is O or another value, it is to ensure the i.MX force the pin to 0V.

Vincent

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi again,

R4261 is a 0ohm, it's here to cut the lane and re-route if something goes wrong in the design.

Best regards,

Eric

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

OK, so if an th RT is driving its pin low it cannot really be detected as it is a direct short circuit.

If you configure this pin as a GPIO, in input mode, do you still have the issue?:

Vincent

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

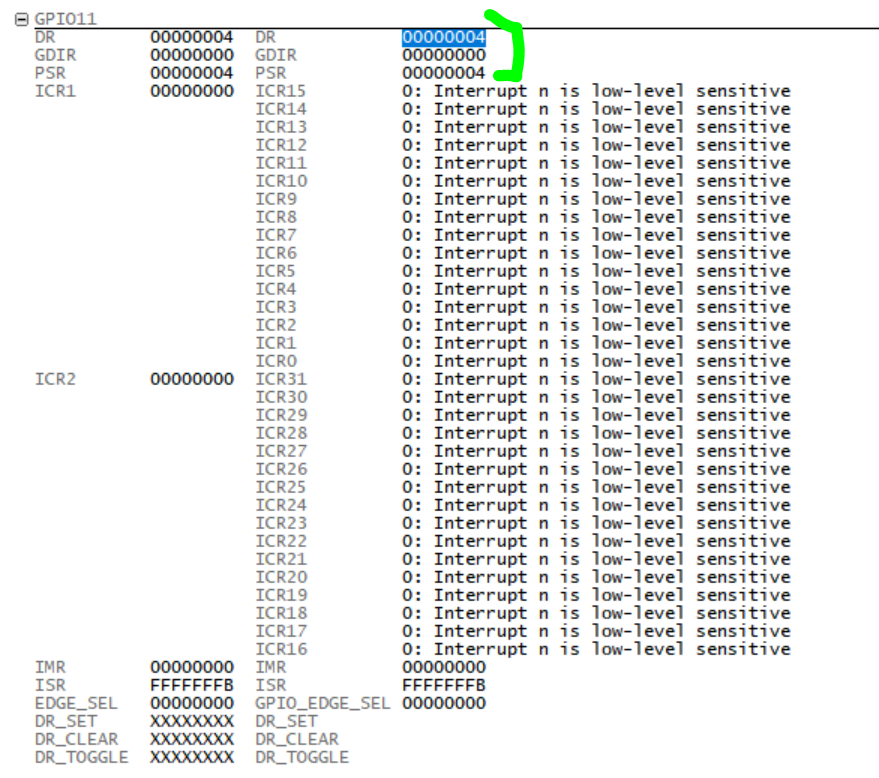

If I configure DISP_B2_01 as GPIO5_02 the level is correct on the lane !

That means the issue come from the SAI configuration.

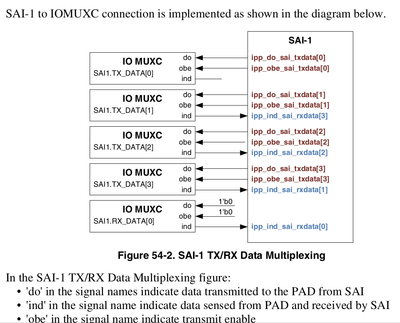

There is this diagram in the SAI documentation.

TX_DATA2 is used for sai_rxdata2 if "obe" is 0 but there is no information about this "obe". My thought was that it is configured by register TCR4 on bits TCE "Transmit Channel Enable"

And as I posted TCR4 is 0x10010f3b so TCE is 0x1 (TX0 enable, other are disabled)

Any information about that ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Also you said that " It is not possible to have hard pull-down in this case."

We already tried to remove it and it does not help

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @mike_susen ,

We don't actually have DAB feature implemented.

But I'll ask hardware guys to patch my board to get FM data on GPIO_DISP_B2_00.

I will also ask hardware guys to connect the microphone (currently GPIO_DISP_B2_06) on GPIO_DISP_B2_01.

Best regards,

Eric

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告