- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: NXP i.MX8QM TJA1101 AUTO-PHY link is not up

NXP i.MX8QM TJA1101 AUTO-PHY link is not up

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

I am working on Ethernet with IMX8QM Custom platform.

Ethernet: TJA1101 AUTO-PHY

Board: IMX8QM Custom Platform

Got log,

[ 2.043859] fec 5b040000.ethernet: Adding to iommu group 1

[ 2.120525] fec 5b040000.ethernet: Invalid MAC address: 00:00:00:00:00:00

[ 2.127330] fec 5b040000.ethernet: Using random MAC address: 8a:c9:99:3f:4f:24

[ 2.145291] mdio_bus 5b040000.ethernet-1: MDIO device at address 1 is missing.

[ 2.152853] fec 5b040000.ethernet eth0: registered PHC device 0

[ 2.166432] hns3: Hisilicon Ethernet Network Driver for Hip08 Family - version

[ 2.200606] igb: Intel(R) Gigabit Ethernet Network Driver

[ 39.454726] NXP TJA1101 5b040000.ethernet-1:00: attached PHY driver [NXP TJA1101] (mii_bus:phy_addr=5b040000.ethernet-1:00, irq=POLL)

And link is not detected,

root@root:~# ifconfig eth0

eth0 Link encap:Ethernet HWaddr 8A:C9:99:3F:4F:24

UP BROADCAST MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

root@root:~# ethtool eth0

Settings for eth0:

Supported ports: [ TP ]

Supported link modes: 100baseT1/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: 100baseT1/Full

Advertised pause frame use: Symmetric

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 100Mb/s

Duplex: Full

Auto-negotiation: off

master-slave cfg: forced master

Port: Twisted Pair

PHYAD: 0

Transceiver: external

MDI-X: Unknown

Supports Wake-on: g

Wake-on: d

Link detected: no

SQI: 0/7

I unable to get the ethernet link is up once connect ethernet cable with board and this is my configuration,

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

fsl,magic-packet;

/* nvmem-cells = <&fec_mac0>;

nvmem-cell-names = "mac-address"; */

status = "okay";

local-mac-address = [32 9f 6f 77 0c 66];

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0>;

/delete-property/ at803x,eee-disabled;

/delete-property/at803x,vddio-1p8v;

/delete-property/phy-supply;

/* at803x,eee-disabled;

at803x,vddio-1p8v;*/

/*tja110x,refclk_in; */

};

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <1>;

at803x,eee-disabled;

at803x,vddio-1p8v;

};

};

};

pinctrl_fec1: fec1grp {

fsl,pins = <

IMX8QM_COMP_CTL_GPIO_1V8_3V3_ENET_ENETB_PAD 0x000014a0

IMX8QM_ENET0_MDC_CONN_ENET0_MDC 0x06000020

IMX8QM_ENET0_MDIO_CONN_ENET0_MDIO 0x06000020

IMX8QM_ENET0_RGMII_TX_CTL_CONN_ENET0_RGMII_TX_CTL 0x06000061

IMX8QM_ENET0_RGMII_TXC_CONN_ENET0_RCLK50M_IN 0xce000061

IMX8QM_ENET0_RGMII_TXD0_CONN_ENET0_RGMII_TXD0 0x06000061

IMX8QM_ENET0_RGMII_TXD1_CONN_ENET0_RGMII_TXD1 0x06000061

IMX8QM_ENET0_RGMII_RX_CTL_CONN_ENET0_RGMII_RX_CTL 0x06000061

IMX8QM_ENET0_RGMII_RXD0_CONN_ENET0_RGMII_RXD0 0x06000061

IMX8QM_ENET0_RGMII_RXD1_CONN_ENET0_RGMII_RXD1 0x06000061

IMX8QM_ENET0_RGMII_RXD2_CONN_ENET0_RMII_RX_ER 0x0d000061

>;

};

Vinothkumar Sekar

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Please close this ticket.

It is a hardware issue.

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

set your device as master like this:

#echo 1 > /sys/devices/platform/soc@0/30800000.bus/30be0000.ethernet/mdio_bus/30be0000.ethernet-1/30be0000.ethernet-1:00/configuration/master_cfg

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you @AlfTeleco ,

I already did, it is the hardware issue and resolve by the hardware engineer.

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

By the way, I am currently debugging an ethernet-phy problem.

We are also using the TJA1101B in a setup with two custom IMX8MP boards.

Both are configured as AUTO_OP using pin strapping.

Once they are at linux, one is set as master ( echo 1 > master_cfg ) and the other remains as slave.

I assing IP to the eth0 iface and I can ping perfectly.

The problem comes when I reset the slave-phy board, the system prompts this trace at boot:

#mdio_bus 30be0000.ethernet-1: MDIO device at address 0 is missing.

#fec 30be0000.ethernet eth0: Unable to connect to phy

It seems that as long as a link between phys exists, the slave will fail to be detected by the system at boot.

Any idea on this? Thanks in advance!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @AlfTeleco ,

Defined mac address under uboot env. if problem still exists define mac address under linux dts

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

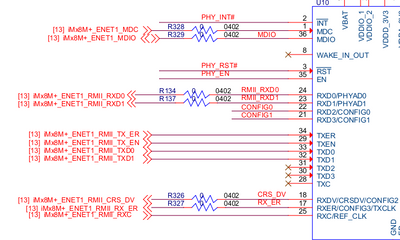

Hi Vinothkumar

one can check "PHYADDRESS" settings as in example on p.23 SPF-29420 MCIMX8QM-CPU

schematic MCIMX8QM-CPU MEK – Schematics

use below dts

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

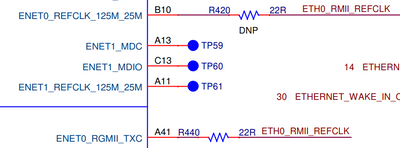

Thank you @igorpadykov for the reply,

Currently TJA1101 AUTO-PHY connect with phy0 of the IMX8QM custom board.

I am doubt about clock,

ENET0_REFCLK_125M_25M I cannot use because it is DNP.

For phy Master, Which one I have to configure (CLOCK_IN or CLOCK_OUT) ENET0_RGMII_TXC ?

IMX8QM_ENET0_RGMII_TXC_CONN_ENET0_RCLK50M_IN

(or)

IMX8QM_ENET0_RGMII_TXC_CONN_ENET0_RCLK50M_OUT

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Please close this ticket.

It is a hardware issue.

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

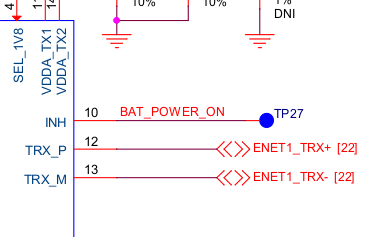

I'm trying to integrate TJA1101 Phy with IMX8M Custom board as 2 -wire ethernet interface. I'm also not able to get the link up.

root@imx8mpevk:/opt/imx8-isp/bin# ethtool eth0

Settings for eth0:

Supported ports: [ TP ]

Supported link modes: 100baseT1/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: 100baseT1/Full

Advertised pause frame use: Symmetric

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 100Mb/s

Duplex: Full

Auto-negotiation: off

master-slave cfg: forced slave

Port: Twisted Pair

PHYAD: 0

Transceiver: external

MDI-X: Unknown

Supports Wake-on: g

Wake-on: d

Link detected: no

SQI: 0/7

root@imx8mpevk:/opt/imx8-isp/bin#&fec {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec>;

phy-mode = "rmii";

phy-handle = <ðphy1>;

fsl,magic-packet;

status = "okay";

phy-reset-gpios = <&gpio3 0 0>;

phy-reset-duration = <10>;

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy1: ethernet-phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0>;

tja110x,refclk_in;

};

};

};

pinctrl_fec: fecgrp {

fsl,pins = <

MX8MP_IOMUXC_SAI1_RXD2__ENET1_MDC 0x3

MX8MP_IOMUXC_SAI1_RXD3__ENET1_MDIO 0x3

MX8MP_IOMUXC_SAI1_RXD4__ENET1_RGMII_RD0 0x91

MX8MP_IOMUXC_SAI1_RXD5__ENET1_RGMII_RD1 0x91

MX8MP_IOMUXC_SAI1_TXD7__ENET1_TX_ER 0x1f

MX8MP_IOMUXC_SAI1_TXD4__ENET1_RGMII_TX_CTL 0x1f

MX8MP_IOMUXC_SAI1_TXD0__ENET1_RGMII_TD0 0x1f

MX8MP_IOMUXC_SAI1_TXD1__ENET1_RGMII_TD1 0x1f

MX8MP_IOMUXC_SAI1_TXFS__ENET1_RGMII_RX_CTL 0x91

MX8MP_IOMUXC_SAI1_TXD6__ENET1_RX_ER 0x1f

MX8MP_IOMUXC_SAI1_MCLK__ENET1_TX_CLK 0x3

/* MX8MP_IOMUXC_SAI1_RXD6__ENET1_RGMII_RD2 0x91 */

/* MX8MP_IOMUXC_SAI1_RXD7__ENET1_RGMII_RD3 0x91 */

/* MX8MP_IOMUXC_SAI1_TXC__ENET1_RGMII_RXC 0x91 */

/* MX8MP_IOMUXC_SAI1_TXD2__ENET1_RGMII_TD2 0x1f */

/* MX8MP_IOMUXC_SAI1_TXD3__ENET1_RGMII_TD3 0x1f */

/* MX8MP_IOMUXC_SAI1_TXD5__ENET1_RGMII_TXC 0x1f */

/* MX8MP_IOMUXC_SAI1_RXD0__GPIO4_IO02 0x19 */

>;

};Im able to set the static IPs in 2 identical boards and not able to ping.

Is there any application/utility for read/write the PHY registers.

Also we have provided an ESD and common mode filter . Could you please confirm if its the same case with yours?

Any help is appreciated.

Regards

Amal