- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: MIPI DSI panel resolution on i.MX 7Dual

MIPI DSI panel resolution on i.MX 7Dual

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MIPI DSI panel resolution on i.MX 7Dual

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

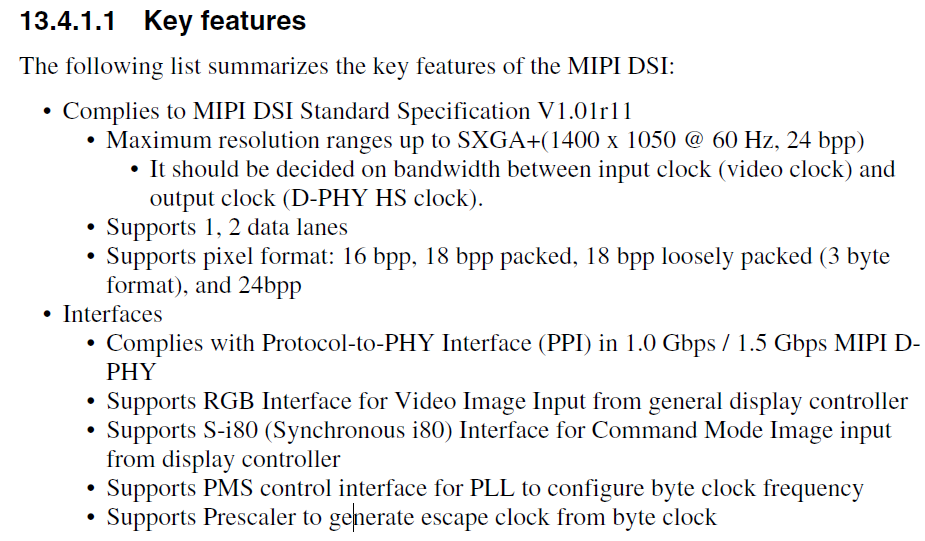

The i.MX7 Reference Manual says the MIPI DSI resolution ranges up to SXGA+(1400 x 1050 @ 60 Hz, 24 bpp).

Is the x-res of 1400 an absolute limit or can this be higher if the y-res is lower than 1050?

I am trying to drive a LCD with a resolution of 1440x240 @ 60Hz, 24bpp using a custom MIPI DSI to RGB converter connected to the DSI port on the i.MX 7Dual Sabre dev board, but I see no RGB data on the DSI data lanes. If I change the driver and device tree configuration to 640x240, the data lanes have RGB data.

Any help/clarification would be appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chris,

See i.MX7D reference manual, please!

We can see "It should be decided on bandwidth between input clock (video clock) and

output clock (D-PHY HS clock)."

For 1440x240 @ 60Hz, 24bpp, The clock it requires is more less than 1.5Gbps, so in theory, your application should be no problem. According to the reference manual, we can ensure the correctness of several standard resolutions listed. You can try to verify several other non-standard resolutions by yourself.

However, in practical applications, it is recommended that the horizontal resolution should not exceed 1400 and the vertical resolution should not exceed 1050.

Hope above information can help you!

Have a nice day!

Best Regards,

NXP TIC team Weidong Sun

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wigros,

Thanks for your reply.

Am I right to assume then that the DSI line buffer is not limited to 1400 x 24bpp? The reference manual refers to the DSI line buffer but does not give the actual size.

For my application, the D-PHY HS clock is running at 150Mhz. This is based on 2 data lanes and a required pixel clock of 25Mhz. The total horizontal samples and vertical lines including blanking is 1500x276. Does this look correct?

Thanks and best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Charis,

See below, please!

>>Am I right to assume then that the DSI line buffer is not limited to 1400 x 24bpp? The reference manual refers to the DSI line buffer but does not give the actual size.

It only requires that MIPI DSI PHY clock could not be more than 1.5Gbps, no other limitations. I have confirmed it with i.MX Expert team.

>>For my application, the D-PHY HS clock is running at 150Mhz. This is based on 2 data lanes and a required pixel clock of 25Mhz. The total horizontal samples and vertical lines including blanking is 1500x276. Does this look correct?

(1) for your application, you only need to focus on the pixclock, the pixclock value x 8 is D-PHY clock, which is far less than 1.5 Gbps.

(2) About MIPI DIS drivers in LINUX BSP for i.MX7D

---device tree: imx7d.dtsi --> imx7d-sdb.dts--->imx7d-sdb-mipi.dts

---drivers

A. drivers/video/fbdev/mxc/mipi_dsi_samsung.c ---- mipi dsi driver of i.MX7D

B. drivers/video/fbdev/mxc/mxcfb_hx8363_wvga.c----lcd driver with MIPI DSI interface

if you want to driver your own LCD, you should change lcd timings in the file.

Have a nice day!

BR,

Weidong