- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- JTAG_MOD Pull Down Resistor Requirements for MX RT1010

JTAG_MOD Pull Down Resistor Requirements for MX RT1010

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

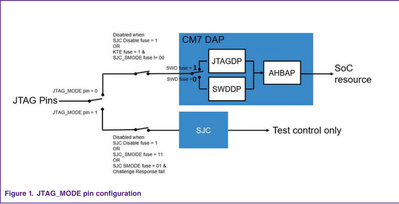

I am using pin GPIO_AD_11 as GPIO25 to connect to a pin of another chip. The pin on the other chip is required to be pulled up but according to the Hardware Development Guide, GPIO_AD_11 needs to be externally pulled down for JTAG_MOD, which is the ALT7 muxing mode for GPIO_AD_11.

The Reference Manual says, "The ALT7 and ALT6 extended muxing modes allow any signal in the system (such as fuse, pad input, JTAG, or software register) to override any software configuration and to force the ALT6/ALT7 muxing mode." I am not quite sure when the JTAG_MOD signal overrides the GPIO signal I have set for the GPIO_AD_11 pad, but I would guess it happens on reset?

My question is, do I really need to externally pull GPIO_AD_11 low? I set GPIO_AD_11 to have a 22k pull up in my software and I am guessing that if the sampling of JTAG_MOD happens at reset (which occurs before my software enables this pull up), that GPIO_AD_11 will have the default 100k pull down resistor enabled when JTAG_MOD is sampled. Is the internal 100k pull down resistor enough to properly set JTAG_MOD? Or do I really need to externally pull it down for some reason.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

I hope you are well.

If SWD/JTAG is going to be used then I suggest you reserve this pin to JTAG_MOD leaving it to GND. It is needed that it is externally terminated by a PD 4.7k resistor or connecting it directly to GND.

Best regards,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for the explanation. Why does it need an external pull down? From the diagram you posted, it seems like as long is the level is low it should be fine.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

By the external termination, we ensure that the pin stays in that state even in noisy environments.

You can connect the pin directly to GND without the need of an external resistor.

Best regards,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Ok that makes sense

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

I hope you are well.

If SWD/JTAG is going to be used then I suggest you reserve this pin to JTAG_MOD leaving it to GND. It is needed that it is externally terminated by a PD 4.7k resistor or connecting it directly to GND.

Best regards,

Omar