- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- IMX8M LPDDR4 choice and hw design

IMX8M LPDDR4 choice and hw design

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all,

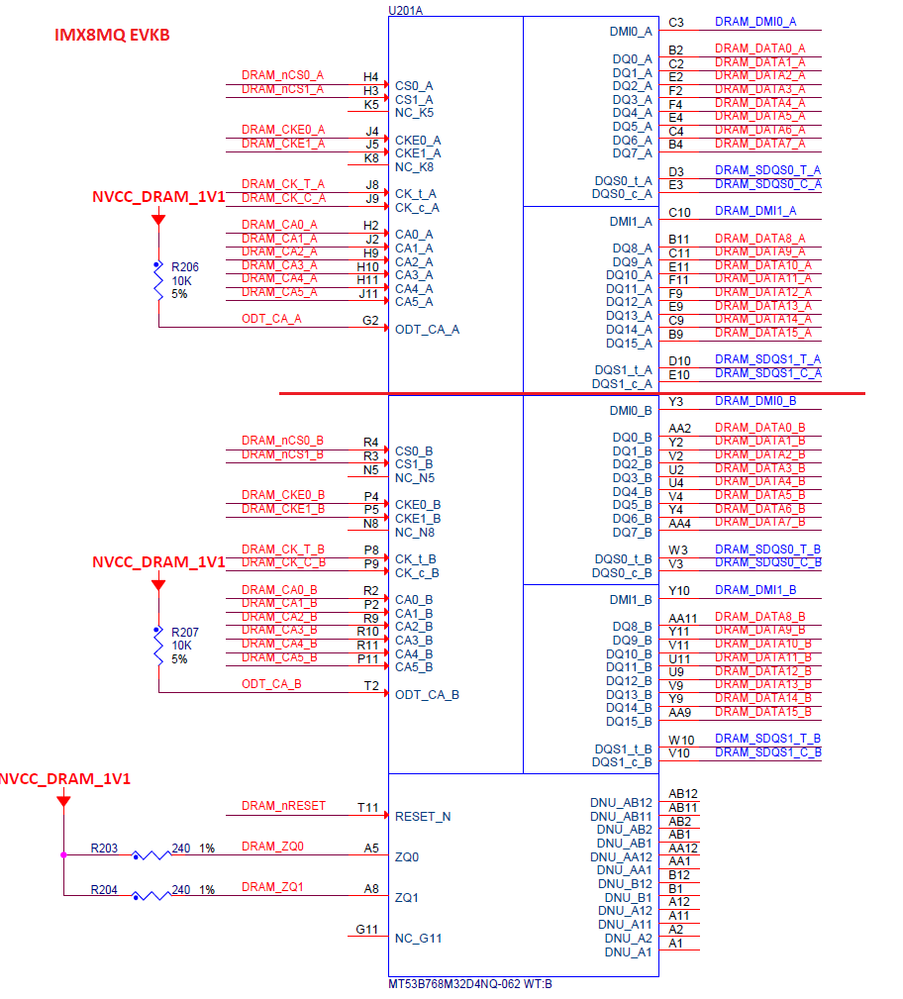

I have IMX8MQ EVKB board which uses 3GB MT53E768M32D4 LPDDR4 ram and another IMX8MM EVK board which uses 2GB (MT53D512M32D2) LPDDR4 ram.

I found these rams are pin, clock and power compatible so I think I can use 2GB MT53D512M32D2 for my all IMX8MQ and IMX8MM boards. But, when I check the reference schematics I found that IMX8MM EVK board have reversed A/B channels. CPU's A channel is connected to RAM's B channel and CPU's B channel is connected to RAM's A channel. Plese check the reference schematics below. I think this is done because of making routing easy. A and B channels works symmetrically. Am I right?

If so, I can route all my IMX8MM and IMX8MQ CPUs and MT53D512M32D2 RAMs and may be MT53E768M32D4 RAMs straight. A<->A, B<->B. Could you correct me?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Yes you're correct Channel A/B were swapped on i.MX8MM EVK for easier signal routing.

There should be no problem swapping back A/B in your design. Also, it may be useful for you to take a look to the HDG for the i.MX 8M & 8MM for reference.

i.MX 8MDQLQ Hardware Developer’s Guide

i.MX 8M Mini Hardware Developer’s Guide

Regards,

Aldo.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, I already have these docs. Thank you for reply

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Yes you're correct Channel A/B were swapped on i.MX8MM EVK for easier signal routing.

There should be no problem swapping back A/B in your design. Also, it may be useful for you to take a look to the HDG for the i.MX 8M & 8MM for reference.

i.MX 8MDQLQ Hardware Developer’s Guide

i.MX 8M Mini Hardware Developer’s Guide

Regards,

Aldo.