- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

How to enable PLL2-SSC funcion of i.MX6Q?

I want to use the Spread Spectrum funcfion for the EMC exam.

However, information of activation can not be found anywhere.

It is considered to be valid if i use the "CCM_ANALOG_PLL_SYS_SS register".

So,I want to know the role of each Bit(Stop/Step/Enable).

Do you have information?

Hi,

I found the below information in the RM.

This PLL synthesizes a low jitter clock from the 24 MHz reference clock. The PLL has

one output clock, plus 3 PFD outputs. The System PLL supports spread spectrum

modulation for use in applications to minimize radiated emissions. The spread spectrum

PLL output clock is frequency modulated so that the energy is spread over a wider

bandwidth, thereby reducing peak radiated emissions. Due to this feature support, the

associated lock time of this PLL is longer than other PLLs in the SoC that do not support

spread spectrum modulation.

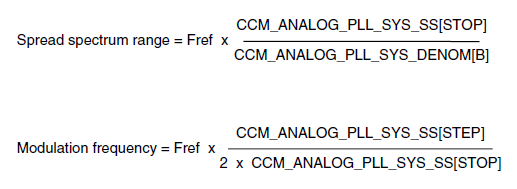

Spread spectrum operation is controlled by configuring the

CCM_ANALOG_PLL_SYS_SS register. When enabled, the PLL output frequency will

decrease by the amount defined in the STEP field, until it reaches the limiting frequency

in the STOP field. The frequency will then similarly return to the original nominal

frequency. The following equations control the spread-spectrum operation:

I wonde if you saw this information.

Unfortunately I could not find any example of it.

Maybe the SDK might be a good base to work.

Best Regards,

Alejandro