- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

Explanation of pixel-bitrate, CSI1_PHY_REF clk and CSI1_CORE clk from MIPI-CSI2 in i.MX8M?

Hi,

I'm porting a new MIPI 4-lane camera with bayer raw format to i.MX8M. But the image doesn't come out. I would like to know the relationship between pixel-rate and the settings of IMX8MQ_CLK_CSI1_PHY_REF_SRC and IMX8MQ_CLK_CSI1_CORE_SRC.

My camera been configured by follow settings:

- The camera use 4-lanes to output Bayer RAW, DPHY=400MHz, 800Mbps.

- The current pixel rate is: 1920x1080x30fps= 62,208,000 pixels/second.

- The pixel format is RAW8, bitrate is: 62,208,000x8 = 497,664,000bps.

And for the MIPI-CSI2 receiver settings on i.MX8 (fsl-imx8mq.dtsi) is:

- IMX8MQ_CLK_CSI1_CORE_DIV: 266MHz

- IMX8MQ_CLK_CSI1_PHY_REF_DIV: 200MHz

- IMX8MQ_CLK_CSI1_ESC_DIV: 66MHz

Q1. Should the PHY_REF clock be configured by 200MHz, 400MHz or 800MHz, when my camera is running at 400MHz/800Mbps?

Q2. Do you named 4-lane mode by Quad Pixel Mode?

Q3. To set the MIPI-CSI core_clk properly, it should be faster than the actual bitrate at single lane: 496,664,000/4 = 124,416,000bps, or just faster than 496,664,000bps?

Q4. According to this thread, I could modify device tree and IMX8MQ_CLK_CSI1_CORE_SRC by clk-imx8mq.c?

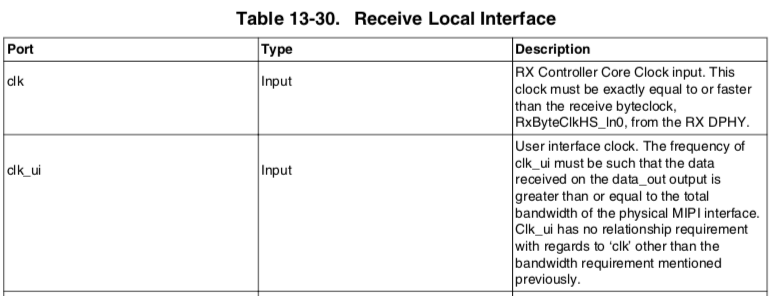

I'm studying the reference manual, and got confused by clk, clk_ui descriptions and the device tree parameters:

Q5. Which clock is mapped to IMX8MQ_CLK_CSI1_CORE_SRC? the clk or clk_ui?

The current progress of my porting is I'm stuck at mx6s_capture.c, so I'm trying to find out if all the clock had been settle properly.

the IRQ handler been triggered several times, but no any image comes to buffer (mx6s_csi_frame_done() not been called ever). And there's no error bit been set in status register (CSI_CSISR).

static irqreturn_t mx6s_csi_irq_handler(int irq, void *data)

{

...

if ((status & BIT_DMA_TSF_DONE_FB1) &&

(status & BIT_DMA_TSF_DONE_FB2)) {

/* For both FB1 and FB2 interrupter bits set case,

* CSI DMA is work in one of FB1 and FB2 buffer,

* but software can not know the state.

* Skip it to avoid base address updated

* when csi work in field0 and field1 will write to

* new base address.

* PDM TKT230775 */

pr_debug("Skip two frames\n");

} else if (status & BIT_DMA_TSF_DONE_FB1) {

mx6s_csi_frame_done(csi_dev, 0, false);

} else if (status & BIT_DMA_TSF_DONE_FB2) {

mx6s_csi_frame_done(csi_dev, 1, false);

}I'm also checked the CSI_CSICR[31:16] for the "frame count", and the value is not zero, and not matched with the frame count inside the output_frame_count register of camera.

Thanks and looking forward for your reply.

i.MX8M processor has 2 MIPI-CSI2 interfaces.

Each one support up to 4 data lanes

It supports from 80Mbps to 1.5Gbps data rate in high speed operation

Amd it supports 10Mbps data rate in low power operation