- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

Hi all,

I have trouble in capture data from FPGA.

My platform: IMX6Q Linux3.0.35

FPGA: YUV422(UYUV) 720P@60fps

IMX6Q: connected with DATA[4]_DATA[19] HS VS PIXCLK VIDEO_EN and use IPU2 CSI1

PIN IOMUX setting :

/* ipu2 csi1 */

MX6Q_PAD_EIM_A16__IPU2_CSI1_PIXCLK,

MX6Q_PAD_EIM_DA11__IPU2_CSI1_HSYNC,

MX6Q_PAD_EIM_DA12__IPU2_CSI1_VSYNC,

MX6Q_PAD_EIM_DA10__IPU2_CSI1_DATA_EN,

MX6Q_PAD_EIM_DA5__IPU2_CSI1_D_4,

MX6Q_PAD_EIM_DA4__IPU2_CSI1_D_5,

MX6Q_PAD_EIM_DA3__IPU2_CSI1_D_6,

MX6Q_PAD_EIM_DA2__IPU2_CSI1_D_7,

MX6Q_PAD_EIM_DA1__IPU2_CSI1_D_8,

MX6Q_PAD_EIM_DA0__IPU2_CSI1_D_9,

MX6Q_PAD_EIM_EB1__IPU2_CSI1_D_10,

MX6Q_PAD_EIM_EB0__IPU2_CSI1_D_11,

MX6Q_PAD_EIM_A17__IPU2_CSI1_D_12,

MX6Q_PAD_EIM_A18__IPU2_CSI1_D_13,

MX6Q_PAD_EIM_A19__IPU2_CSI1_D_14,

MX6Q_PAD_EIM_A20__IPU2_CSI1_D_15,

MX6Q_PAD_EIM_A21__IPU2_CSI1_D_16,

MX6Q_PAD_EIM_A22__IPU2_CSI1_D_17,

MX6Q_PAD_EIM_A23__IPU2_CSI1_D_18,

MX6Q_PAD_EIM_A24__IPU2_CSI1_D_19,

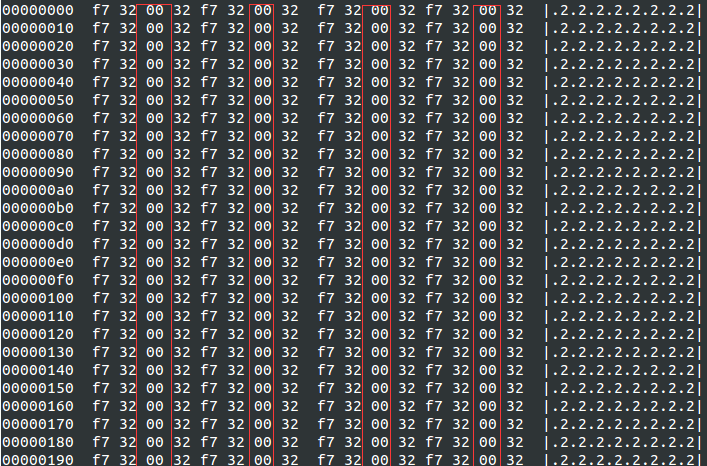

I use GATE Mode to capture stream, and it works. but the data I got was wrong.

The data in red box should be DC, and it always in same wrong in same place.

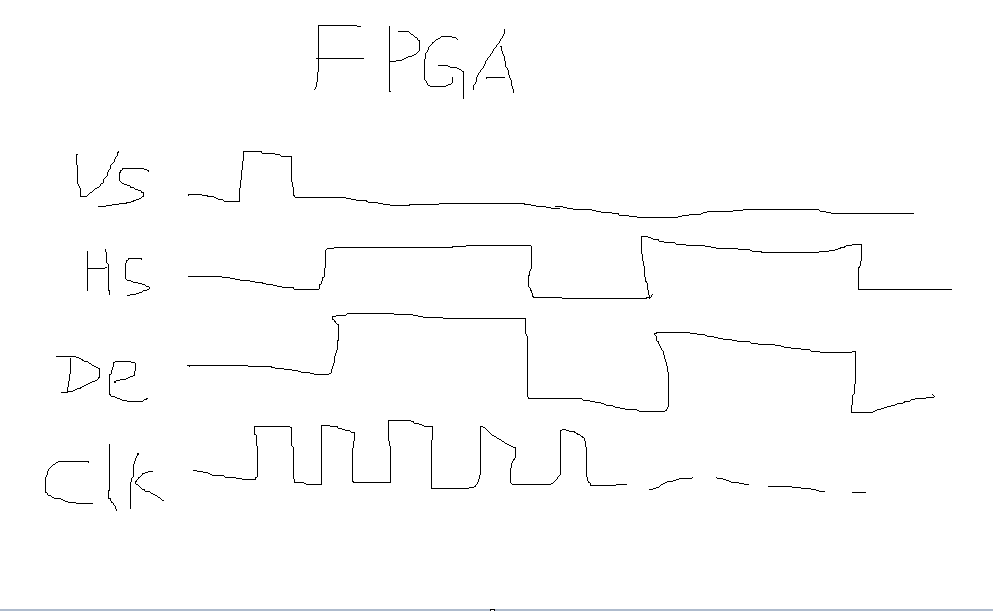

The FPGA wave is like this:

Here is the reigster that I dumped.

imx-ipuv3 imx-ipuv3.1: csi=1, CSI_SENS_CONF = 0x0000CA00

imx-ipuv3 imx-ipuv3.1: csi=1, CSI_ACT_FRM_SIZE=0X02CF04FF

The CPMEM is:

imx-ipuv3 imx-ipuv3.1: ch 1 word 0 - 00000000 00000000 00000000 E0001800 000B3C9F

imx-ipuv3 imx-ipuv3.1: ch 1 word 1 - 03200000 00640000 2147C000 00027FC0 00000000

imx-ipuv3 imx-ipuv3.1: PFS 0xa,

imx-ipuv3 imx-ipuv3.1: BPP 0x3,

imx-ipuv3 imx-ipuv3.1: NPB 0x1f

imx-ipuv3 imx-ipuv3.1: FW 1279,

imx-ipuv3 imx-ipuv3.1: FH 719,

imx-ipuv3 imx-ipuv3.1: EBA0 0x19000000

imx-ipuv3 imx-ipuv3.1: EBA1 0x19000000

imx-ipuv3 imx-ipuv3.1: Stride 2559

imx-ipuv3 imx-ipuv3.1: scan_order 0

imx-ipuv3 imx-ipuv3.1: uv_stride 0

imx-ipuv3 imx-ipuv3.1: u_offset 0x0

imx-ipuv3 imx-ipuv3.1: v_offset 0x0

imx-ipuv3 imx-ipuv3.1: Width0 0+1,

imx-ipuv3 imx-ipuv3.1: Width1 0+1,

imx-ipuv3 imx-ipuv3.1: Width2 0+1,

imx-ipuv3 imx-ipuv3.1: Width3 0+1,

imx-ipuv3 imx-ipuv3.1: Offset0 0,

imx-ipuv3 imx-ipuv3.1: Offset1 0,

imx-ipuv3 imx-ipuv3.1: Offset2 0,

imx-ipuv3 imx-ipuv3.1: Offset3 0

dump ipu after enable csi:

imx-ipuv3 imx-ipuv3.1: IPU_CONF = 0x00000102

imx-ipuv3 imx-ipuv3.1: IDMAC_CONF = 0x0000002F

imx-ipuv3 imx-ipuv3.1: IDMAC_CHA_EN1 = 0x00000002

imx-ipuv3 imx-ipuv3.1: IDMAC_CHA_EN2 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IDMAC_CHA_PRI1 = 0x18800001

imx-ipuv3 imx-ipuv3.1: IDMAC_CHA_PRI2 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IDMAC_BAND_EN1 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IDMAC_BAND_EN2 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_CHA_DB_MODE_SEL0 = 0x00000002

imx-ipuv3 imx-ipuv3.1: IPU_CHA_DB_MODE_SEL1 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_CHA_TRB_MODE_SEL0 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_CHA_TRB_MODE_SEL1 = 0x00000000

imx-ipuv3 imx-ipuv3.1: DMFC_WR_CHAN = 0x00000090

imx-ipuv3 imx-ipuv3.1: DMFC_WR_CHAN_DEF = 0x202020F6

imx-ipuv3 imx-ipuv3.1: DMFC_DP_CHAN = 0x00009694

imx-ipuv3 imx-ipuv3.1: DMFC_DP_CHAN_DEF = 0x2020F6F6

imx-ipuv3 imx-ipuv3.1: DMFC_IC_CTRL = 0x00000002

imx-ipuv3 imx-ipuv3.1: IPU_FS_PROC_FLOW1 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_FS_PROC_FLOW2 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU Warning - IPU_INT_STAT_5 = 0x00000002

imx-ipuv3 imx-ipuv3.1: IPU_FS_PROC_FLOW3 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_FS_DISP_FLOW1 = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_VDIC_VDI_FSIZE = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_VDIC_VDI_C = 0x00000000

imx-ipuv3 imx-ipuv3.1: IPU_IC_CONF = 0x00000000

Any ideas?

已解决! 转到解答。

clock can be adjusted in ../mach-mx6/clock.c for gated mode

may be useful

https://community.nxp.com/docs/DOC-97981

~igor

Hi li

IPU_INT_STAT_5 = 0x00000002 may mean new frame starts before the previous

end-of-frame event as result of data rate problems. Such problems may be a

result of the IPU running in slower clock then required by the use case.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

clock can be adjusted in ../mach-mx6/clock.c for gated mode

may be useful

https://community.nxp.com/docs/DOC-97981

~igor