- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Can't download hello world into M4 in the MCIMX8M-EVK eval board

Can't download hello world into M4 in the MCIMX8M-EVK eval board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can't download hello world into M4 in the MCIMX8M-EVK eval board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

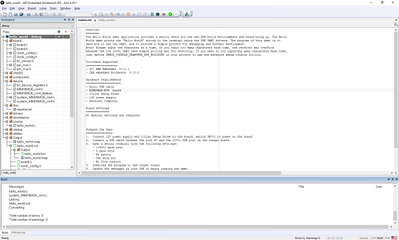

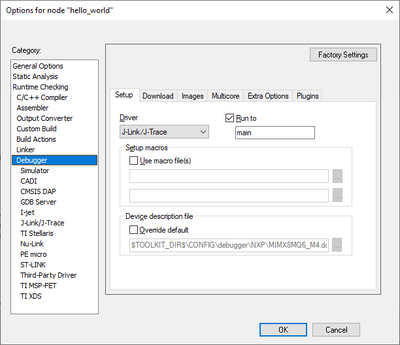

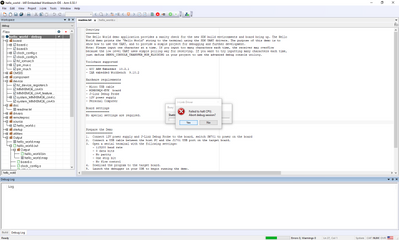

I followed doc "Getting Started with MCUXpresso SDK i.MX 8M Quad" and setup my IAR environment successfully, plus it complied with no error, see image below.

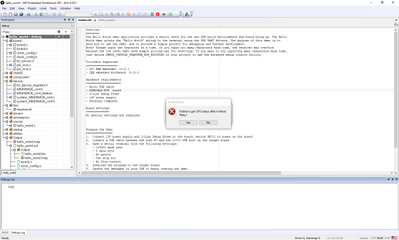

Unfortunately, i couldn't download to the eval board and have the JLink driver message "Failed to get CPU status......", see image below.

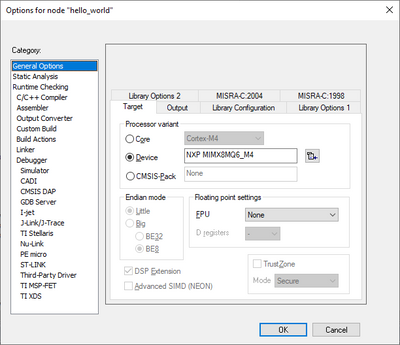

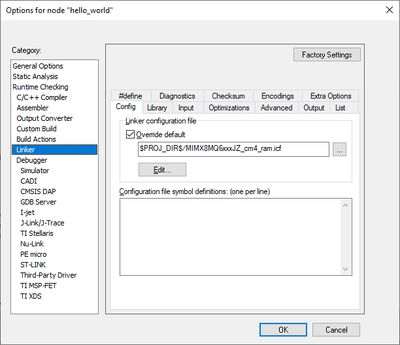

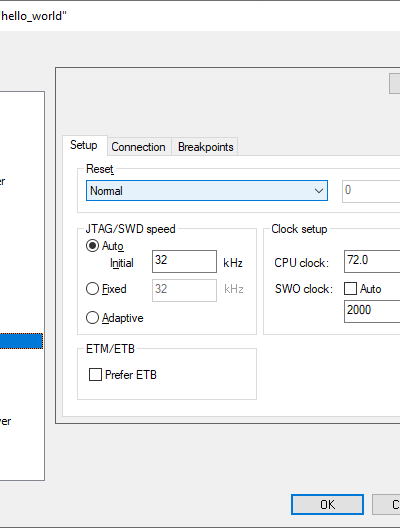

I checked my setup and couldn't find any problem or anything i missed, see the following images.

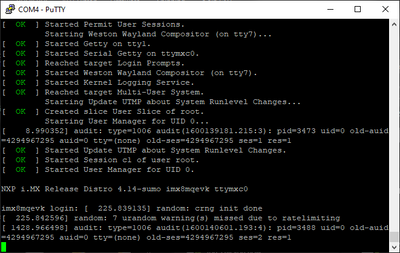

BTW, I opened two terminal to see the debug messages, i have the Linux side showing messages, but not the M4 side, see below.

I am using this SDK version "SDK_2_10_0_EVK-MIMX8MQ".

My goal is first try out a few samples project, such as hello world, mulitcore pingpong and string echo etc., eventually hope i can create messaging function through the remote processor messaging between A53 (Linux) and M4 (maybe RTOS, but not necessary).

Please advise if there is any tips and recommendation.

Thanks in advance!

Gilbert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@gsmgbl

Hello,

please try the following patch:

https://www.nxp.com/webapp/Download?colCode=SDK_MX8MQ_3RDPARTY_Patch&appType=license

Summary Page:

https://www.nxp.com/design/software/embedded-software/i-mx-software:IMX-SW

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

Thanks for your info. In fact, I forgot to mention that i've got the 3rd party SDK already, you may see it from my environment image. Unfortunately, i still couldn't download the binary into the M4.

Do you have other suggestion?

Regards,

Gilbert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

I finally downloaded the binary into the M4 now.

I found that I have a later IAR version 8.50 available, somehow it was using the old version of IAR that causing the problem.

Regards,

Gilbert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

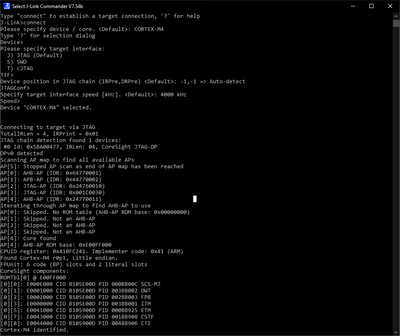

I am able to connect to the M4 core through the JLink commander, see below.

But still having problem to download the hello world binary into the M4, see error message below.

I followed this following page to check the boot switch.

https://www.nxp.com/document/guide/getting-started-with-the-mcimx8m-evk:GS-MCIMX8M-EVK

I also using the linux boot code and boot from SD card, Linux is booting up, but I still couldn't download binary into the M4.

Please advise. Thanks!

Gilbert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the log from IAR while i download the hello world binary.

Fri Oct 01, 2021 10:18:57: IAR Embedded Workbench 8.50.1 (C:\Program Files (x86)\IAR Systems\Embedded Workbench 8.4\arm\bin\armproc.dll)

Fri Oct 01, 2021 10:18:57: Device "CORTEX-M4" selected.

Fri Oct 01, 2021 10:18:57: JLINK command: ProjectFile = C:\Users\GLIU\Desktop\iMX8\EVK\SDK_2_10_0_EVK-MIMX8MQ\boards\evkmimx8mq\demo_apps\hello_world\iar\settings\hello_world_debug.jlink, return = 0

Fri Oct 01, 2021 10:18:57: Device "CORTEX-M4" selected.

Fri Oct 01, 2021 10:18:57: DLL version: V6.62a, compiled Jan 31 2020 12:58:08

Fri Oct 01, 2021 10:18:57: Firmware: J-Link V9 compiled May 7 2021 16:26:12

Fri Oct 01, 2021 10:18:57: JTAG speed is initially set to: 32 kHz

Fri Oct 01, 2021 10:18:57: TotalIRLen = 4, IRPrint = 0x01

Fri Oct 01, 2021 10:18:57: JTAG chain detection found 1 devices:

Fri Oct 01, 2021 10:18:57: #0 Id: 0x5BA00477, IRLen: 04, CoreSight JTAG-DP

Fri Oct 01, 2021 10:18:57: Cannot determine DP version. Assuming DPv0

Fri Oct 01, 2021 10:18:57: Scanning AP map to find all available APs

Fri Oct 01, 2021 10:18:57: AP[5]: Stopped AP scan as end of AP map has been reached

Fri Oct 01, 2021 10:18:57: AP[0]: AHB-AP (IDR: 0x64770001)

Fri Oct 01, 2021 10:18:57: AP[1]: APB-AP (IDR: 0x44770002)

Fri Oct 01, 2021 10:18:57: AP[2]: JTAG-AP (IDR: 0x24760010)

Fri Oct 01, 2021 10:18:57: AP[3]: JTAG-AP (IDR: 0x001C0030)

Fri Oct 01, 2021 10:18:57: AP[4]: AHB-AP (IDR: 0x24770011)

Fri Oct 01, 2021 10:18:57: Iterating through AP map to find AHB-AP to use

Fri Oct 01, 2021 10:18:58: AP[0]: Skipped. No ROM table (AHB-AP ROM base: 0x00000000)

Fri Oct 01, 2021 10:18:58: AP[1]: Skipped. Not an AHB-AP

Fri Oct 01, 2021 10:18:58: AP[2]: Skipped. Not an AHB-AP

Fri Oct 01, 2021 10:18:58: AP[3]: Skipped. Not an AHB-AP

Fri Oct 01, 2021 10:18:58: AP[4]: Core found

Fri Oct 01, 2021 10:18:58: AP[4]: AHB-AP ROM base: 0xE00FF000

Fri Oct 01, 2021 10:18:58: CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

Fri Oct 01, 2021 10:18:58: Found Cortex-M4 r0p1, Little endian.

Fri Oct 01, 2021 10:18:58: FPUnit: 6 code (BP) slots and 2 literal slots

Fri Oct 01, 2021 10:18:58: CoreSight components:

Fri Oct 01, 2021 10:18:58: ROMTbl[0] @ E00FF000

Fri Oct 01, 2021 10:18:58: ROMTbl[0][0]: E000E000, CID: B105E00D, PID: 000BB00C SCS-M7

Fri Oct 01, 2021 10:18:58: ROMTbl[0][1]: E0001000, CID: B105E00D, PID: 003BB002 DWT

Fri Oct 01, 2021 10:18:58: ROMTbl[0][2]: E0002000, CID: B105E00D, PID: 002BB003 FPB

Fri Oct 01, 2021 10:18:58: ROMTbl[0][3]: E0000000, CID: B105E00D, PID: 003BB001 ITM

Fri Oct 01, 2021 10:18:58: ROMTbl[0][5]: E0041000, CID: B105900D, PID: 000BB925 ETM

Fri Oct 01, 2021 10:18:58: ROMTbl[0][7]: E0043000, CID: B105900D, PID: 001BB908 CSTF

Fri Oct 01, 2021 10:18:58: ROMTbl[0][8]: E0044000, CID: B105900D, PID: 004BB906 CTI

Fri Oct 01, 2021 10:18:58: Reset: Halt core after reset via DEMCR.VC_CORERESET.

Fri Oct 01, 2021 10:18:58: Reset: Reset device via AIRCR.SYSRESETREQ.

Fri Oct 01, 2021 10:18:58: Reset: S_RESET_ST never gets cleared. CPU seems to be kept in reset forever.

Fri Oct 01, 2021 10:18:58: Reset: Using fallback: Reset pin.

Fri Oct 01, 2021 10:18:58: Reset: Halt core after reset via DEMCR.VC_CORERESET.

Fri Oct 01, 2021 10:18:58: Reset: Reset device via reset pin

Fri Oct 01, 2021 10:18:59: Reset: VC_CORERESET did not halt CPU. (Debug logic also reset by reset pin?).

Fri Oct 01, 2021 10:18:59: Reset: Reconnecting and manually halting CPU.

Fri Oct 01, 2021 10:18:59: Cannot determine DP version. Assuming DPv0

Fri Oct 01, 2021 10:18:59: AP map detection skipped. Manually configured AP map found.

Fri Oct 01, 2021 10:18:59: AP[0]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:18:59: AP[1]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:18:59: AP[2]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:18:59: AP[3]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:18:59: AP[4]: AHB-AP (IDR: Not set)

Fri Oct 01, 2021 10:18:59: AP[4]: Core found

Fri Oct 01, 2021 10:18:59: AP[4]: AHB-AP ROM base: 0xE00FF000

Fri Oct 01, 2021 10:18:59: CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

Fri Oct 01, 2021 10:18:59: Found Cortex-M4 r0p1, Little endian.

Fri Oct 01, 2021 10:18:59: Warning: CPU could not be halted

Fri Oct 01, 2021 10:18:59: Reset: Core did not halt after reset, trying to disable WDT.

Fri Oct 01, 2021 10:18:59: Reset: Halt core after reset via DEMCR.VC_CORERESET.

Fri Oct 01, 2021 10:18:59: Reset: Reset device via reset pin

Fri Oct 01, 2021 10:19:00: Reset: VC_CORERESET did not halt CPU. (Debug logic also reset by reset pin?).

Fri Oct 01, 2021 10:19:00: Reset: Reconnecting and manually halting CPU.

Fri Oct 01, 2021 10:19:00: Cannot determine DP version. Assuming DPv0

Fri Oct 01, 2021 10:19:00: AP map detection skipped. Manually configured AP map found.

Fri Oct 01, 2021 10:19:00: AP[0]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:19:00: AP[1]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:19:00: AP[2]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:19:00: AP[3]: MEM-AP (IDR: Not set)

Fri Oct 01, 2021 10:19:00: AP[4]: AHB-AP (IDR: Not set)

Fri Oct 01, 2021 10:19:00: AP[4]: Core found

Fri Oct 01, 2021 10:19:00: AP[4]: AHB-AP ROM base: 0xE00FF000

Fri Oct 01, 2021 10:19:00: CPUID register: 0x410FC241. Implementer code: 0x41 (ARM)

Fri Oct 01, 2021 10:19:00: Found Cortex-M4 r0p1, Little endian.

Fri Oct 01, 2021 10:19:00: Warning: CPU could not be halted

Fri Oct 01, 2021 10:19:01: Warning: CPU could not be halted

Fri Oct 01, 2021 10:24:15: IAR Embedded Workbench 8.50.1 (C:\Program Files (x86)\IAR Systems\Embedded Workbench 8.4\arm\bin\armproc.dll)