- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Can I read/write TLP packet including 512 Bytes payload via PCIe in i.MX6?

Dear All,

I want to read/write large TLP packet.

I read this post.

https://community.nxp.com/message/350342

It have been concluded that max payload is 128 byte.

I understood CX_MAX_MTU, CC_SLV_MTU and CC_MSTR_BURST_LEN are fixed.

If I change Max_Payload_Size and Max_Read_Request_Size in PCIE_RC_DConR, then can I process TLP packet including 512 byte payload with PCIe in i.MX6?

Best Regards,

Regarding to the PCIe RC driver contained in NXP Linux BSP, there is one outbound region used to access the CFG space of PCIe EP.The outbound TLP would be issued, when the

PCIe EP CFG IO APIs(imx_pcie_rd_conf/imx_pcie_wr_conf) are called by PCIe EP driver.

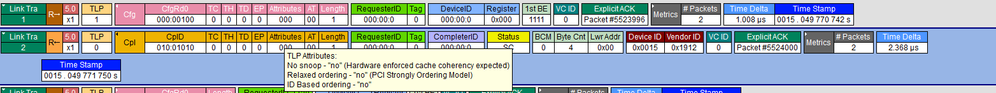

The following is the snapshot of the PCIe protocol analyzer.

One outbound TLP when the CFG space of PCIe EP is accessed.

Dear jamesbone,

Thank you for your reply.

I cannot decide that my understanding is correct or not, you say, driver of PCIe RC have only one region and it is for CFG space of PCIe EP, it cannot keep CFG data of PCIe RC in i.MX6. CFG space of PCIe RC in i.MX6 can be accessed only from PCIe EP, ARM CPU in i.MX6 is cannot change it.

That is that I cannot change Max_Payload_Size and Max_Read_Request_Size, and I cannot change max payload size of TLP packet of PCIe in i.MX6 from 128bytes.

Do I mistake them?

Best Regards,