- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

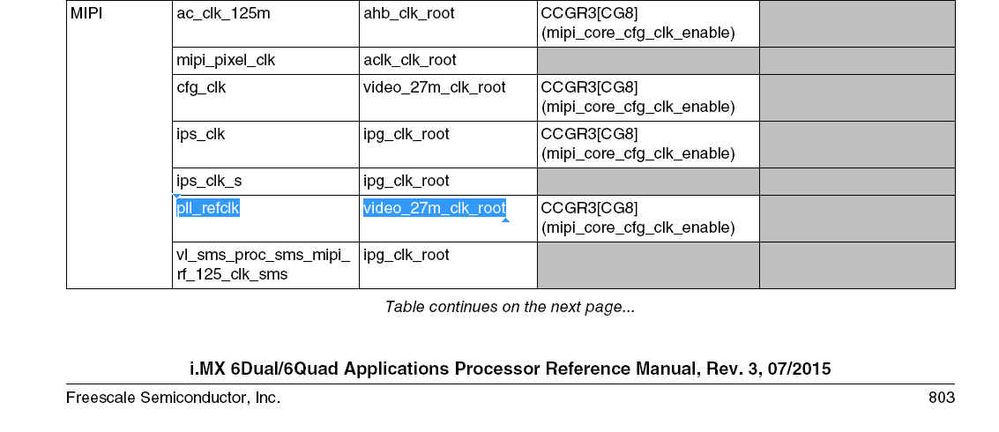

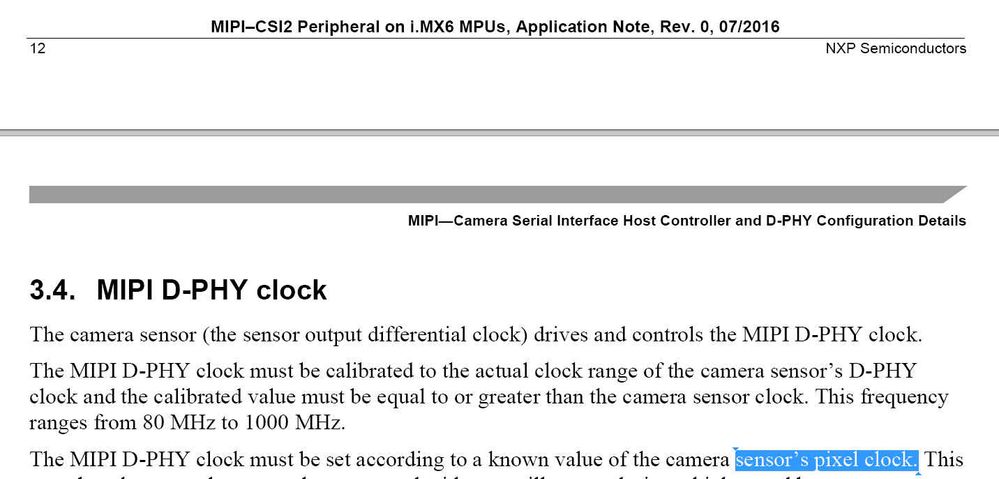

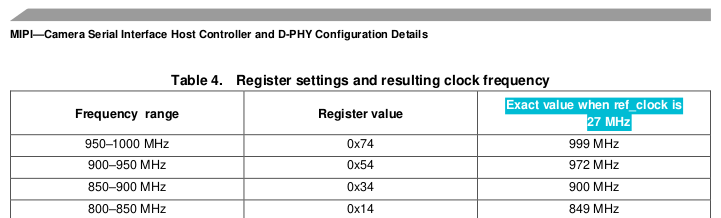

From the reference manual on "MIPI-CSI2 Peripheral on i.MX6 MPUs", AN5305 - MIPI CSI2, table 4 shows register values for... some clock - it's not specific. The values are based on a ref_clock of 27MHz. However, the default clock is 24 MHz for the YOCTO build.

How is the table generated?

已解决! 转到解答。

>The actual clock is 24MHz

mipi pll_refclk can not be 24MHz by design, please refer to parts of i.MX6DQ Reference Manual, pll_refclk can be only 27MHz,

24MHz can not be sourced to mipi pll_refclk by design

i.MX6DQ Reference Manual

http://www.nxp.com/docs/en/reference-manual/IMX6DQRM.pdf

Best regards

igor

Hi Nate

24MHz is crystal reference clock and other clocks (including 27MHz) are produced

by plls as described in Figure 18-2. Clock Tree i.MX6DQ Reference Manual

http://www.nxp.com/docs/en/reference-manual/IMX6DQRM.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thanks for reviewing my question!

How are the register values calculated for MIPI_CSI_PHY_TST_CTRL1 ? There is a nice table in both IMX6DQRM and AN5305 (table 4), but no explanation on how the table is calculated. Could you help me with that?

one can also look at

Debug steps for customer MIPI sensor.docx

Table values are not calculated, seems they are provided by designers

based on modelling MIPI-CSI module.

Best regards

igor

Hi Nate

what bsp used in the case, if it third party, you can also post questions on meta-fsl-arm mailing list

https://lists.yoctoproject.org/listinfo/meta-freescale

Best regards

igor

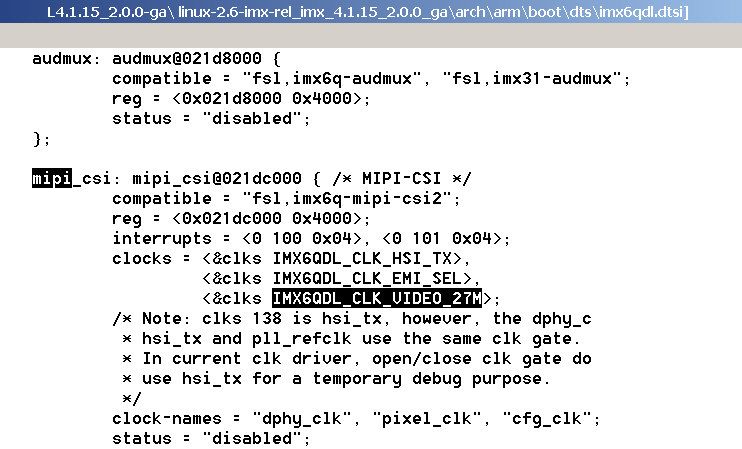

The kernel is from codearora which was included in the Yocto build. Line 71 in drivers/clk/imx/clk-imx6q.c,

static const char *cko1_sels[] = { "pll3_usb_otg", "pll2_bus", "pll1_sys", "pll5_video_div",

"video_27m", "axi", "enfc", "ipu1_di0", "ipu1_di1", "ipu2_di0",

"ipu2_di1", "ahb", "ipg", "ipg_per", "ckil", "pll4_audio_div", };

Notice that I changed the 4th entry to video_27m. I also updated the parent clock for cko1 to be video_27m,

@@ -1012,8 +1012,8 @@ static void __init imx6q_clocks_init(struct device_node *ccm_node)

* Let's initially set up CLKO with OSC24M, since this configuration

* is widely used by imx6q board designs to clock audio codec.

*/

- imx_clk_set_parent(clk[IMX6QDL_CLK_CKO2_SEL], clk[IMX6QDL_CLK_OSC]);

- imx_clk_set_parent(clk[IMX6QDL_CLK_CKO], clk[IMX6QDL_CLK_CKO2]);

+ imx_clk_set_parent(clk[IMX6QDL_CLK_CKO1_SEL], clk[IMX6QDL_CLK_VIDEO_27M]);

+ imx_clk_set_parent(clk[IMX6QDL_CLK_CKO], clk[IMX6QDL_CLK_CKO1]);

/* Audio-related clocks configuration */

clk_set_parent(clk[IMX6QDL_CLK_SPDIF_SEL], clk[IMX6QDL_CLK_PLL3_PFD3_454M]);

there is no need for these changes as "video_27m" is already configured in dts

imx6qdl.dtsi\dts\boot\arm\arch - linux-imx - i.MX Linux kernel

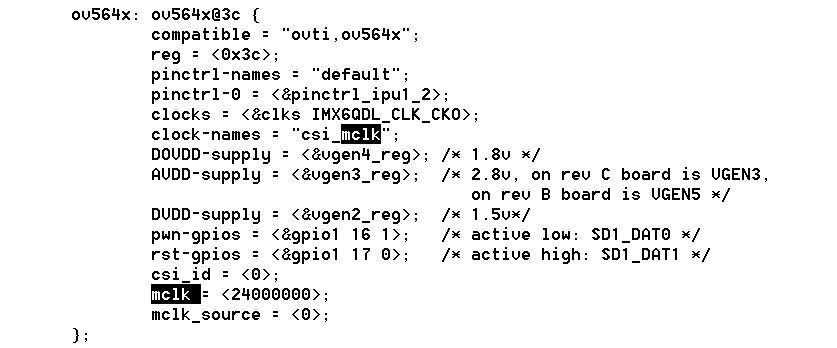

probably there is confusion regarding "24MHz" as it is used only as reference clock for ov5640 sensor,

mclk in dts file. OV5640 uses it for own plls and produces pixel clock which then used in AN5305 calculations

Yes, Igor, I see the same. But this is NOT true when booted. Take a look at /sys/kernel.debug/clk/clk_summary

Here, clearly, cko is NOT 27MHz but rather 24MHz. You must take a look at the clock settings in drivers/clk/mxc/clk-imx6q.c

To my main question, if the sensor clock is 24MHz (NOT 27MHz) then what are the calculations for table 4 in the AN5305 - MIPI CSI2 documentation?

Hi Nate

>To my main question, if the sensor clock is 24MHz (NOT 27MHz) then what are the

>calculations for table 4 in the AN5305 - MIPI CSI2 documentation?

it does not matter what is sensor reference clock, as it can be any - sensor reference clock

is used only for generating pixel clock. Pixel clock is used for calculations in AN5305,

not sensor reference clock.

Best regards

igor

Sorry but you English is too broken up. The section you are pointing to is exactly what I'm trying to figure out. Notice that in the following image that the ref_clock is set to 27MHz. The actual clock is 24MHz.

How are these calculated?

>The actual clock is 24MHz

mipi pll_refclk can not be 24MHz by design, please refer to parts of i.MX6DQ Reference Manual, pll_refclk can be only 27MHz,

24MHz can not be sourced to mipi pll_refclk by design

i.MX6DQ Reference Manual

http://www.nxp.com/docs/en/reference-manual/IMX6DQRM.pdf

Best regards

igor

Yes, I think you are right. In my effort to be thorough, I got them confused.

><

At least in our application, speed is important. I just needed to be certain that the details were right. Thank you igorpadykov!