- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- ADV7280-m clock issue

ADV7280-m clock issue

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

ADV7280-m clock issue

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello.

Currently I am working on driver integration task for adv7280-m chip.

And I got issue related to mipi csi clock. Mipi dphy driver detect Clock line as ULPS(ultralow power state). You can see my oscilloscope images in this branch adv7280-M clock problem | EngineerZone .

I am trying to understand what could be the reason of issue: adv7280-m chip or imx6. Could anybody, who worked with this adv7280-m chip show me your signals on the mipi lines or analize my signals.

I also interested in what should be switched on first: the decoder chip mipi dphy or imx6 mipi dphy.

As I understand. there are a lot of people who managed to get workable adv7280-m chip with imx6. Could you also share your mipi csi2 driver settup

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have not adv7280 but one can attach external termination resistors and check.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Unfortunately it is difficult to solder this termination resistor on our board. May be we will order ADV7280-m kit and connect it to CM-FX6 kit or Sabre board.

Could you explane me some points related to MIPI_CSI_PHY_STATE.

First of all 9-th bit. Active low. Is that mean that clk lane in ULPS if the bit equel zero value?

8-th bit. Clock lane actively receiving a DDR cloclk. Is that bit mean(1-value) that imx6 DPHY module clock is correctly configured. In my case it is always zero value.

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

please create new thread for new questions

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fan

I would suggest to configure properly i.MX6 mipi clock as described in

Debug steps for customer MIPI sensor.docx

A Simple tutor for writing i.MX6 mipi driver, use adv7480 as an example

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor.

Do you think it is correct that transition from 1.2V to 0.1-0,2V on CLK line was detected as ULPS by imx6(0x210 in state register)?

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I think yes it can be detected in MIPI_CSI_PHY_STATE register bit 9.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

But ULPS mode should have 0V level on lines. In our case we have 0,1-0,2V and it is high speed level according to DPHY specification.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

are you sure that this is not noise, as is ULPS mode

sensor can turn off supplies from lane.

Also this can be quality issue, so recommended to double

check behaviour on other board/sensor.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As I understand, imx6 should detect 1.2 >0.1V transition(low power -> high speed) and set termination on the line. If it detect this transition as ULPS, it of course will not set termination and future signal on the line will be not correct(noise in my case as you said).

Do you have any opportunity to get signal oscilloscope images in case of correct imx6-adv7280-m work?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello.

Thank you for replay. I will examine the experience and patches for adv7480.

Do you know whether I will see mipi clk sygnal on the clk wire in case of wrong mipi clock configuration in imx6 processor?

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

actually adi support suggested easy way to debug that

as described in AN1337 on p.2:

manually program the clock lane of the ADV7280-M, ADV7281-M

to enter and then exit LP mode. The easiest way to do this is by

toggling the CSITX_PWRDN bit (Address 0x00, Bit 7).

Data and clock lanes can enter ulps state independently, for clock lane

one can follow comand given on p.52

also please check

i.MX6Q video capture issue with ADV7280-M

~igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I of course tried all of these debug steps.

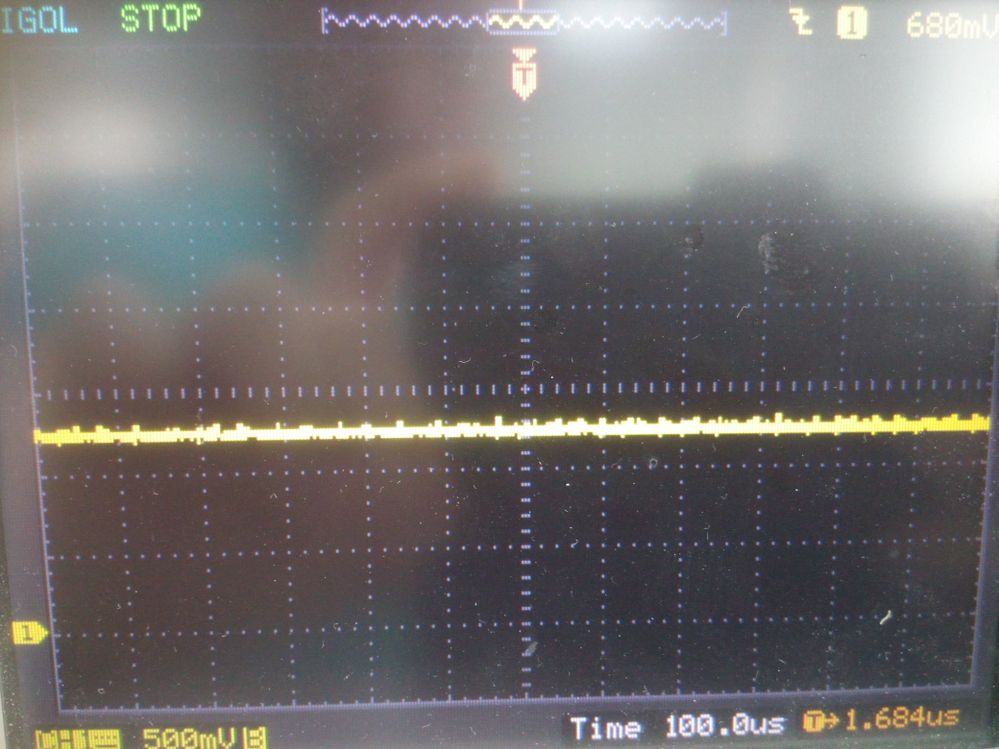

See below my oscilloscope images.

1) Low state mode: CSITX_PWRDN bit (Address 0x00, Bit 7) contains 1 value.

Mipi data:

Mipi clk:

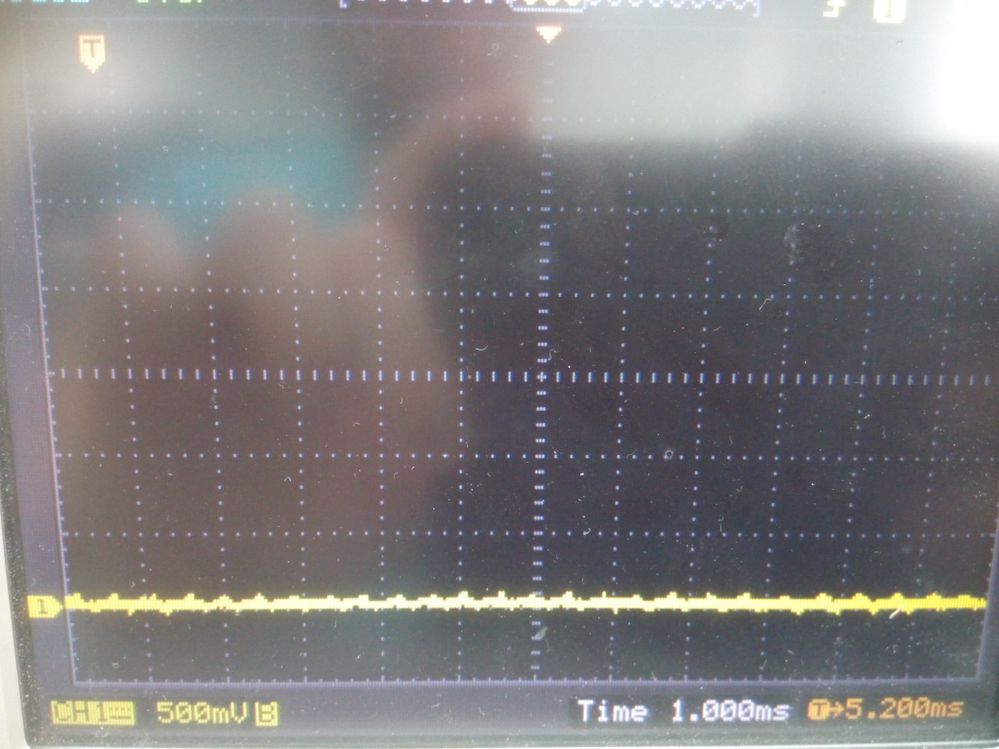

2) Switching on to high speed mode: set CSITX_PWRDN bit (Address 0x00, Bit 7) in zero value.

Mipi data in high speed mode:

Mipi clk in high speed mode:

Transient process from low power to high speed on mipi clk line:

If I switch on imx6 dphy(mipi_csi2_reset()) after clearing CSITX_PWRDN in ad7280-m, I get 0x200 in State register. If I switch on imx6 dphy before clearing CSITX_PWRDN, I get 0x210 in State register.

3) Just for experience: set both lines to ULPS mode, regarding to ADV7280_7281_7282_UG-637.pdf documet P.52

For both lines:

You can see, that MIPI lines pulled down in real ULPS mode.

I also looked through this brunch i.MX6Q video capture issue with ADV7280-M.

But I think my problem is a little be different, as I can`t see clk sygnal physically. There could be several reasons for this issue:

1) imx6 incorrect terminates mipi clk line. To exclude this version, It could be useful if anybody could show his mipi clk sygnal in case of switched off imx6 dphy and switched on dphy.

2) ad7280 incorrect pass clk sygnal. To exclude this issue I need to get example of clean mipi sygnal from ADV7280-m with disconnected from mipi slave device wires.

3) hardware issue on my board

Than you for help.