- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Wireless Connectivity

- :

- Setting CLK_OSC32M_DIV to 0 results in runtime error

Setting CLK_OSC32M_DIV to 0 results in runtime error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Setting CLK_OSC32M_DIV to 0 results in runtime error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello team,

My customer is trying to maximize the throughput of the processor, by minimizing the clock's divisions.

please find his inquires below:

1) My specific question is: how to change the CLK_OSC32M_DIV register from its default value of 1 to 0: from 16 Mhz to 32 Mhz.

What I am trying to do is:

CLOCK_SetClkDiv(kCLOCK_DivOsc32mClk, 0U);

Which results in a runtime error.

2) Additionally, if you could spot some more clock division settings that I am missing, I would appreciate it.

I couldn't attach his project but he used GPIO Driver example code from the QN9080 SDK.

Please advise back and stay safe.

Thanks and regards,

Shai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shai, I hope you're doing well!

Unfortunately, I wasn't able to replicate the issue your customer is having.

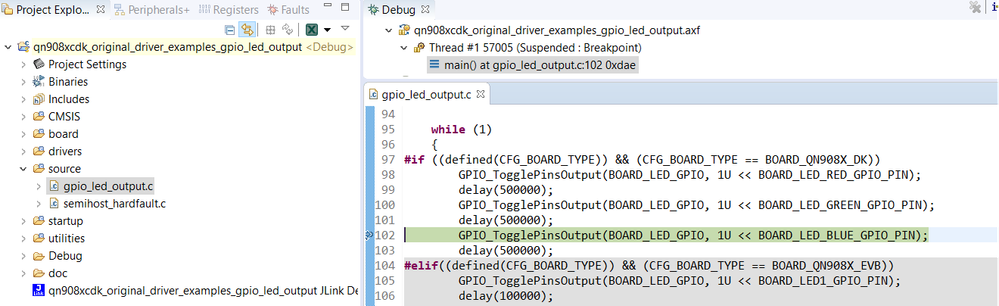

I changed the call to the CLOCK_SetClkDiv inside of the BOARD_BootClockRUN function (which is called of main, in the gpio_led_output.c source file) to the following:

CLOCK_SetClkDiv(kCLOCK_DivOsc32mClk, 0U);

Could you please tell me where was this line changed? Or if any other changes were done to the code?

There are other existing clock division settings, each managing one of the different clocks. These can also be seen in the BOARD_BootClockRUN function I mentioned previously, but the clock divider you're changing should be the only needed function for this purpose.

Please let me know if you need any more information.

Best regards,

Sebastian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shai,

I imported the attached project to my MCUXpresso installation and unfortunately I still wasn't able to replicate the issue:

Could you please let me know if your customer is using our QN9080-DK board or if they are using a custom board?

Best regards,

Sebastian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sebastián,

Yes, the customer is using the QN9080-DK board.

Do you need any additional information from my side to address this issue?

Thanks in advance

Kind regards,

Shai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content