- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Wireless Connectivity

- :

- Re: K32W061 Coder Read Protection Guide

K32W061 Coder Read Protection Guide

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

K32W061 Coder Read Protection Guide

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm starting a new product development using a K32W061 uC. And I'm pretty lost with the management of the Code Read Protection, boot, SWD, and ISP.

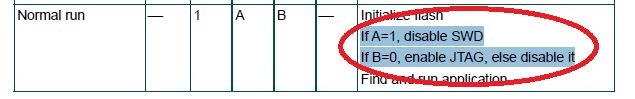

At the K32W061 there is the following table:

Reading this table, in the "Normal run2 mode:

I can't understand why these two diferent ways of describing SWD and the JTAG enabling fields. What happend if A=0? I suppose SWD is enable, but it makes me doubt. Is it possible SWD session in "Normal Mode (PIO0_5 high)" ?

Apart, unfortunetly I was not able to find how and where can I set these Flash fields SWD_DIS, and JTAG_DIS. On the other hand, Hardware Test Mode Enable is decribed on pFlash, together with ISP access level, but again I was not able to find a propper descrition of this pFlash and how to setup. The only description I found was on the section "38.7.6 Set ISP access level to write-only" using raw ISP. Does the DK6programmer have an easier support to setup the pFalsh?

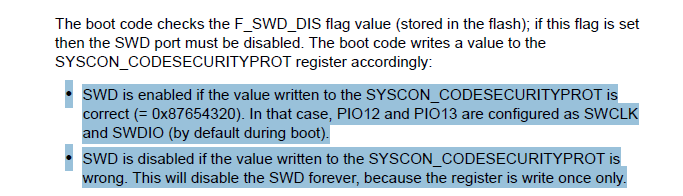

Finally, about the code read protection, the user manual mentions the following:

And in some SDK examples, I found the following code:

/* Board pin init */

/* Security code to allow debug access */

SYSCON->CODESECURITYPROT = 0x87654320;

but, also this other code on "startup_k32w061.c" using a LPC code read protection style. I guess this is a SDK bug:

#if (defined(__MCUXPRESSO))

#include <NXP/crp.h>

__CRP const unsigned int CRP_WORD = CRP_NO_CRP;

#endif

and on crp.h:

#define __CRP __attribute__ ((used,section(".crp")))

#define CRP_NO_CRP 0xFFFFFFFF

// Disables UART and USB In System Programming (reads and writes)

// Leaves SWD debugging, with reads and writes, enabled

#define CRP_NO_ISP 0x4E697370

// Disables SWD debugging & JTAG, leaves ISP with with reads and writes enabled

// You will need UART connectivity and FlashMagic (flashmagictool.com) to reverse

// this. Don't even try this without these tools; most likely the SWD flash

// programming will not even complete.

// Allows reads and writes only to RAM above 0x10000300 and flash other than

// sector 0 (the first 4 kB). Full erase also allowed- again only through UART

// and FlashMagic (NO JTAG/SWD)

#define CRP_CRP1 0x12345678

// Disables SWD debugging & JTAG, leaves UART ISP with with only full erase

// enabled. You must have UART access and FlashMagic before setting this

// option.

// Don't even try this without these tools; most likely the SWD flash

// programming will not even complete.

#define CRP_CRP2 0x87654321So, I was not able to have a clear understanding of the managment of these subjects. Is there any appnote with a deeper explanation of all this things?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Javier, I hope you're doing well!

I'm sorry for the inconvenience this may cause, but currently all of the information about CRP (Code Read Protection) that is available to share is the one found in the user manuals.

We are continuously working to provide more information about the modules in these new devices.

Just to clarify, in the case you describe, A = 0 will enable SWD. In normal circumstances without changes to SWD_DIS and JTAG_DIS, the device is able to be programmed using both SWD and JTAG.

Still, the DK6 programmer may be useful to provide control and setup for the flash on these devices.

Please let me know if you need any more information.

Best regards,

Sebastián