- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Sensors Knowledge Base

- :

- FXLS8471Q - FIFO Fill mode example code

FXLS8471Q - FIFO Fill mode example code

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

FXLS8471Q - FIFO Fill mode example code

FXLS8471Q - FIFO Fill mode example code

Hi Everyone,

I would like to share here one of my examples I created for the FXLS8471Q accelerometer while working with the Freescale FRDM-KL25Z platform and FRDM-FXS-MULT2-B sensor expansion board. It illustrates the use of the embedded FIFO buffer to collect the 14-bit acceleration data that are read from the FIFO using an interrupt technique through the SPI interface. For details on the configurations of the FIFO buffer as well as more specific examples and application benefits, please refer to the AN4073.

The FXLS8471Q is initialized as follows:

void FXLS8471Q_Init (void)

{/* The software reset does not work properly in SPI mode as described in Appendix A of the FXLS8471Q data sheet. Therefore the following piece of the code is not used. I have shortened R46 on the FRDM-FXS-MULTI-B board to activate a hardware reset. FXLS8471Q_WriteRegister(CTRL_REG2, 0x40); // Reset all registers to POR values */

FXLS8471Q_WriteRegister(CTRL_REG1, 0x00); // Standby mode

FXLS8471Q_WriteRegister(F_SETUP_REG, 0xA0); // FIFO Fill mode, 32 samples

FXLS8471Q_WriteRegister(CTRL_REG4, 0x40); // Enable FIFO interrupt, push-pull, active low

FXLS8471Q_WriteRegister(CTRL_REG5, 0x40); // Route the FIFO interrupt to INT1 - PTA5

FXLS8471Q_WriteRegister(CTRL_REG1, 0x19); // ODR = 100Hz, Active mode

}

In the ISR, only the interrupt flag is cleared and the FIFO_DataReady variable is set to indicate that the FIFO is full.

void PORTA_IRQHandler()

{

PORTA_PCR5 |= PORT_PCR_ISF_MASK; // Clear the interrupt flag

FIFO_DataReady = 1;

}

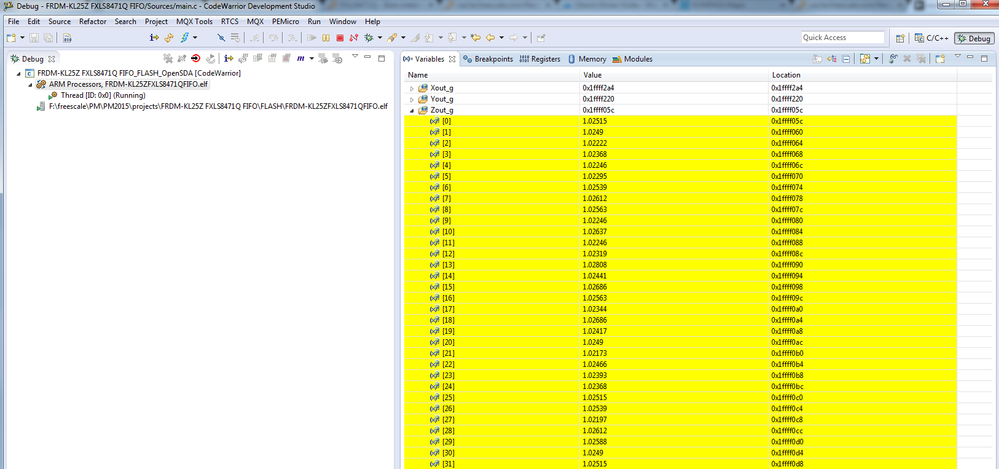

Once the FIFO_DataReady variable is set, the STATUS register (0x00) is read to clear the FIFO interrupt status bit and deassert the INT1 pin. Afterwars the FIFO is read using a 192-byte (3 x 2 x 32 bytes) burst read starting from the OUT_X_MSB register (0x01). Then the raw acceleration data are converted to signed 14-bit values and real values in g’s.

if (FIFO_DataReady)

{

FIFO_DataReady = 0;

FIFO_Status = FXLS8471Q_ReadRegister(STATUS_REG); // Read the Status register to clear the FIFO interrupt status bit

FXLS8471Q_ReadMultiRegisters(OUT_X_MSB_REG, 6*Watermark_Val, AccelData); // Read the FIFO using a burst read

for (i = 0; i < Watermark_Val; i++)

{

// 14-bit accelerometer data

Xout_Accel_14_bit[i] = ((short) (AccelData[0 + i*6]<<8 | AccelData[1 + i*6])) >> 2; // Compute 14-bit X-axis acceleration output values

Yout_Accel_14_bit[i] = ((short) (AccelData[2 + i*6]<<8 | AccelData[3 + i*6])) >> 2; // Compute 14-bit Y-axis acceleration output values

Zout_Accel_14_bit[i] = ((short) (AccelData[4 + i*6]<<8 | AccelData[5 + i*6])) >> 2; // Compute 14-bit Z-axis acceleration output values

// Accelerometer data converted to g's

Xout_g[i] = ((float) Xout_Accel_14_bit[i]) / SENSITIVITY_2G; // Compute X-axis output values in g's

Yout_g[i] = ((float) Yout_Accel_14_bit[i]) / SENSITIVITY_2G; // Compute Y-axis output values in g's

Zout_g[i] = ((float) Zout_Accel_14_bit[i]) / SENSITIVITY_2G; // Compute Z-axis output values in g's

}

}

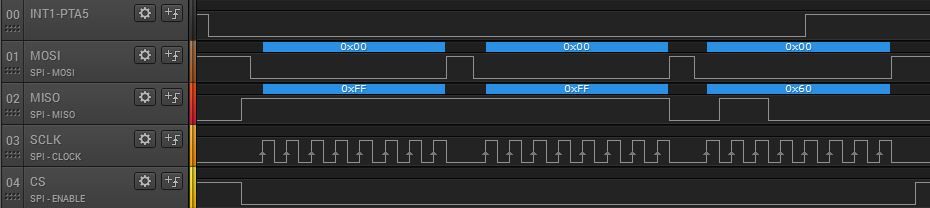

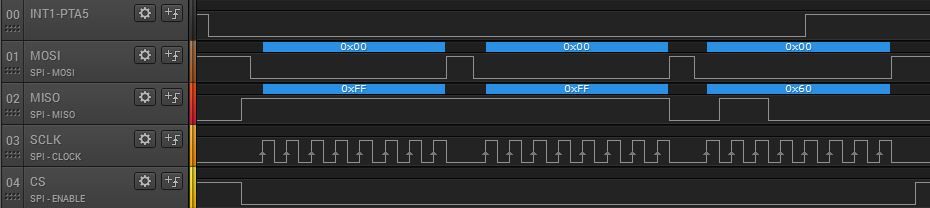

Deassertion of the INT1 pin after reading the STATUS register (0x00).

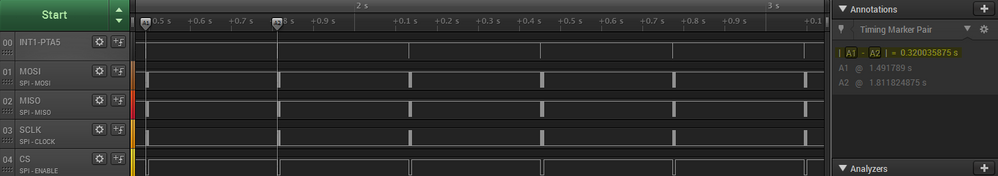

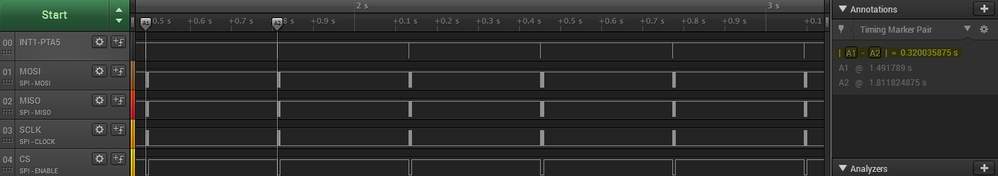

ODR is set to 100Hz, so the FIFO is read every 320 ms (10 ms x 32 samples).

The calculated values can be watched in the "Variables" window on the top right of the Debug perspective.

Attached you can find the complete source code written in the CW for MCU's 10.6. If there are any questions regarding this simple example project, please feel free to ask below. Your feedback or suggestions are also welcome.

Regards,

Tomas

Original Attachment has been moved to: FRDM-KL25Z-FXLS8471Q-FIFO.rar