- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

code can not get data from no_cacheable ram if source code runs in ITCM

hello NXP experts:

I met a question about RAM access.

I modify the link file and locate all the source code in ITCM (all the hex is located from 0x00000000) and I take use of SPI and DMA to communicate with the external device.

when I set the value in global ram and trigger DMA transmit, there is no data in MTSR PIN, if I set a breakpoint after RAM data setting but before DMA transfer. there will be data in MTSR.

so I guess the root cause may be the ram refresh because ITCM runs high frequency than SRAM .

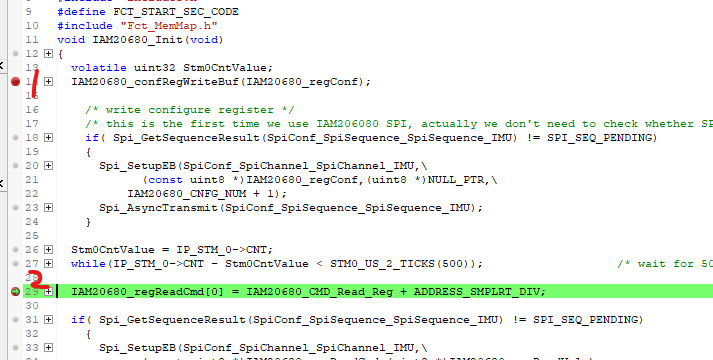

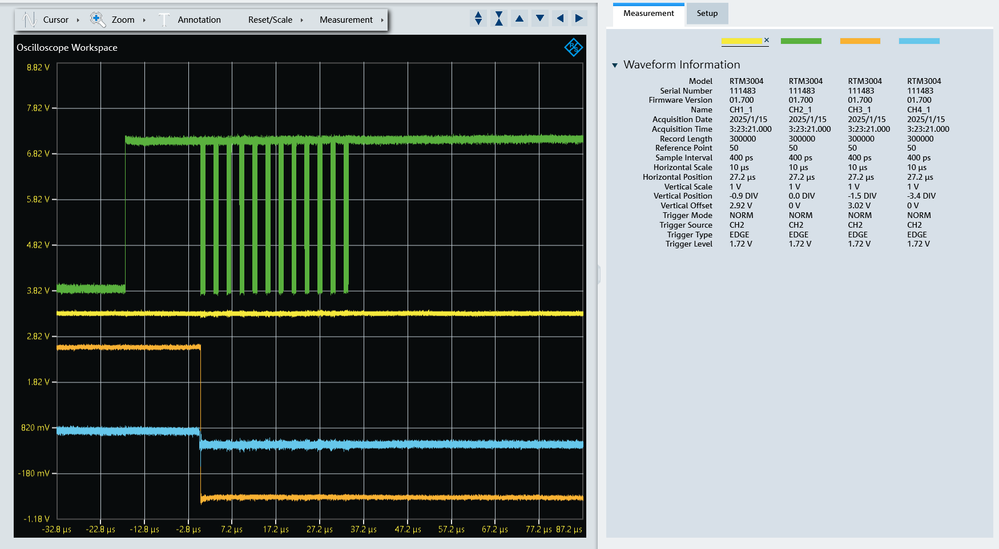

you can check the two pic below, if I go from breakpoint 1 to breakpoint 2 ,there is no contents in the MTSR(orange color)

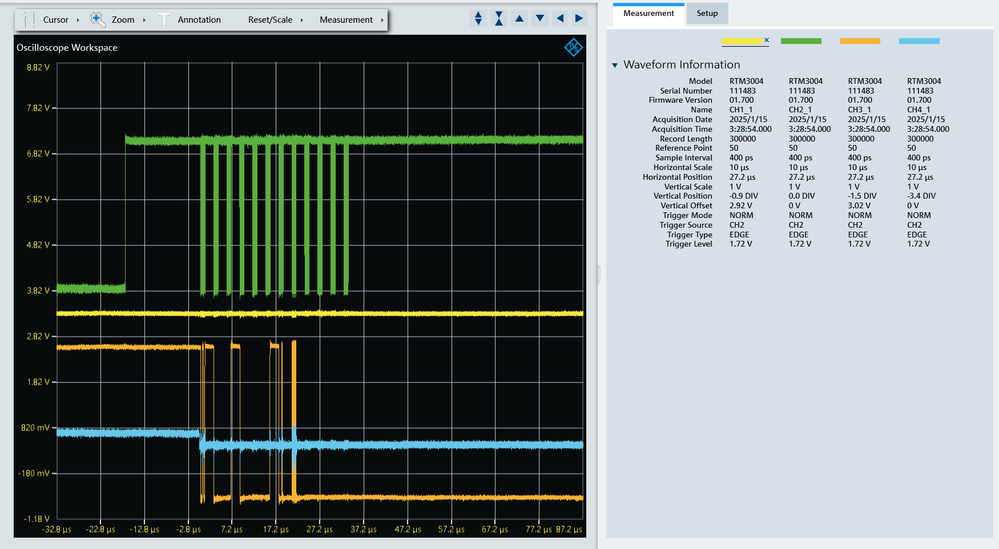

you can check the two pictures below and if I go from breakpoint 1 to breakpoint 2 to breakpoint 3(I just do a stop between breakpoint 1 and breakpoint 3) .

there is contents in the MTSR(orange color).

do you have any solution for this problem .thanks a lot

hi PetrS:

I think I have solved this problem :

because I have to put all source code in RAM and ITCM and DTCM is not large enough to cover all the source code ,so I put some code in shareable ram. but it will report hard fault if instruction access in shareable ram.

I tried to solve this hardfault problem by disable the MPU. but disable the MPU may have some effect on the other area for example no cacheable ram .

now I try to enable MPU again but modify the rasr register for shareable ram and change the value from 0x130C0001UL to 0x030C0001UL

hi PetrS:

in my current project, I disable the MPU function by disable the data setting for "S32_MPU->CTRL " in "system.c".

Will it have any relationship with the current problem?

hi PetrS:

I set the Tx buffer and Rx buffer in the no cacheable ram, it works OK if the source code runs in PFlash

but if I set the code run in ITCM by modify the link file, the SPI seems can not transfer the correct data in MTSR.

I try to solve this problem by init the Tx buffer by data segment rather than bss segment and it works OK because there is no need to init the tx buffer before calling "SPI_SetupEB".

but I still meet a question for getting data in Rx Buffer. sometimes ,I can not get the correct data from Rx buffer event if the contents in MRST pin is correct.(the contents in MRST is 1 but the data in Rx Buffer in 0, but correct 1 is get if a break point is set)