- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32k148 - FTM timer as clock divider

S32k148 - FTM timer as clock divider

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32k148 - FTM timer as clock divider

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Could you please provide sample code how to configure FTM Timer 5 channel 7 as divider of clock coming on TCLK0?

Thank you,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jakub,

I am sorry there is no sample code for FTM5.

But you can try to test it just modify below registers:

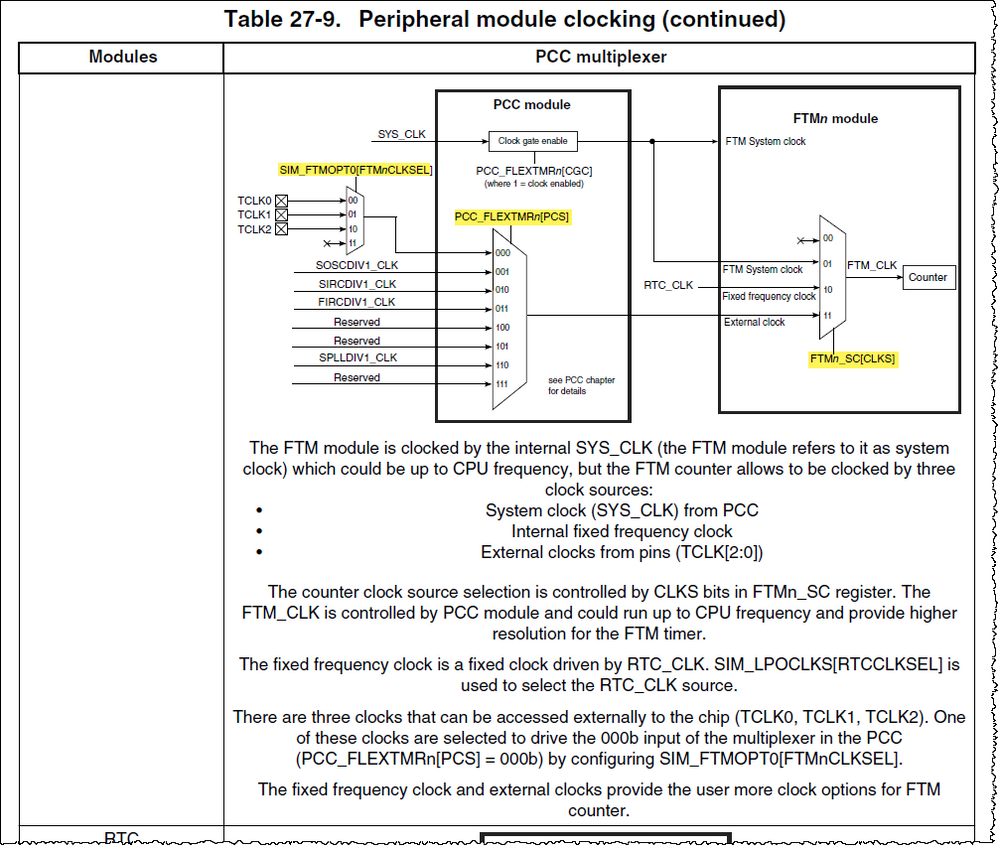

SIM_FTMOPT0[FTMnCLKSEL]=0

PCC_FLEXTMRn[PCS]=0

FTMn_SC[CLKS]=0b11

External clock need to be connect to TCLK0.

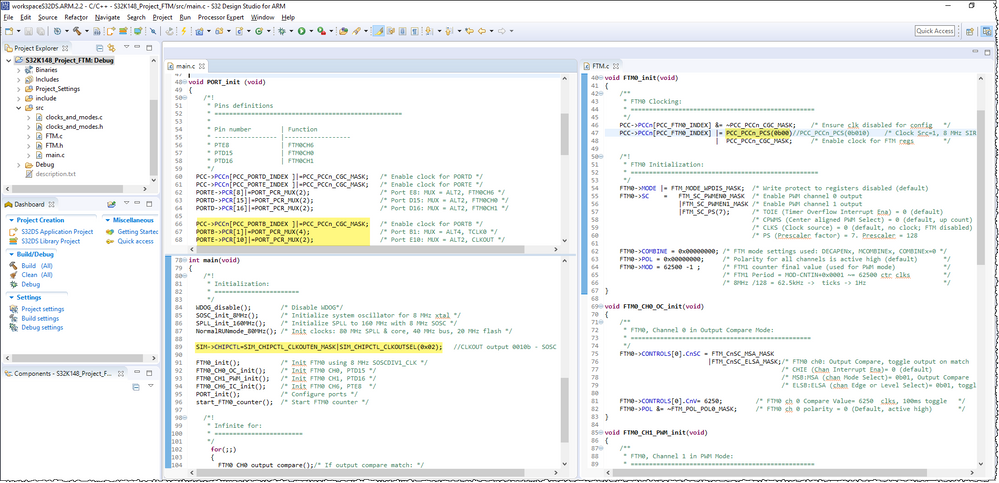

I have test on S32K148_Project_FTM example.

The CLKOUT signal(PTE10) output clock to TCLK0(PTB1), then I can see the FTM0_CH0 output signal.

PCC->PCCn[PCC_PORTB_INDEX ]|=PCC_PCCn_CGC_MASK; /* Enable clock for PORTB */

PORTB->PCR[1]|=PORT_PCR_MUX(4); /* Port B1: MUX = ALT4, TCLK0 */

PORTE->PCR[10]|=PORT_PCR_MUX(2); /* Port E10: MUX = ALT2, CLKOUT */SIM->CHIPCTL=SIM_CHIPCTL_CLKOUTEN_MASK|SIM_CHIPCTL_CLKOUTSEL(0x02); //CLKOUT output 0010b - SOSC DIV2 CLK

PCC->PCCn[PCC_FTM0_INDEX] &= ~PCC_PCCn_CGC_MASK; /* Ensure clk disabled for config */

PCC->PCCn[PCC_FTM0_INDEX] |= PCC_PCCn_PCS(0b00)//PCC_PCCn_PCS(0b010) /* Clock Src=1, 8 MHz SIRCDIV1_CLK */

| PCC_PCCn_CGC_MASK; /* Enable clock for FTM regs */

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin,

Can FTM5 CH7 work as clock divider with up-counting and toggle on output compare?

Best regards,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes

47.4.3.2 Status And Control (SC)

This register will divide clock source from TCLK0.

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you share example FTM5 register settings for this function?