- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

S32K148 LPSPI AUTOPCS

Hi,

I counfig LPSPI1 as slave, LPSPI0 as master ,and LPSPI0 transfer data to LPSPI1,and LPSPI1_AUTOPCS bit is set, TCR[CPHA]=1.The SCK(LPAPI0 produce )remain more than 4 LPSPI clock cycle between word. But when i do not connect LPSPI0_PCS0 to LPSPI1_PCS0, the transfer between LPSPI0 and LPSPI1 is failure,LPSPI1 can't receve data which from LPSPI0.

Whether my understand correctly about ? : LPSPI1_AUTOPCS = 1,and TCR[CPHA]=1,andThe SCK(LPAPI0 produce )remain more than 4 LPSPI clock cycle between word. If the above conditions are met,Even if the LPSPI1_PCS0 not connect to LPSPI0_PCS0,LPSPI can receve data from LPSPI0.

ooking forward to your reply!

Hi @SONGTAOSI,

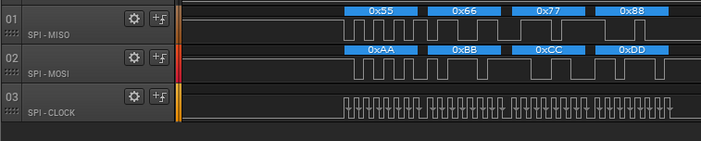

Have you scoped the bus? Can you show the oscillograms?

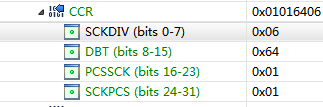

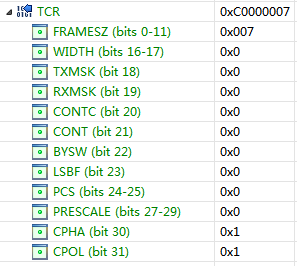

What is the LPSPI functional clock and CCR, TCR configuration?

Have you tried increasing the SCKPCS, PCSSCK or DBT parameters?

Regadrs,

Daniel

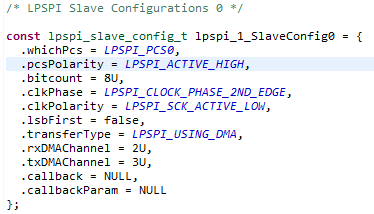

Thanks @SONGTAOSI, this seems to be correct.

Did you configure the polarity of the selected PCS as described here:

Regards,

Daniel

Hello @SONGTAOSI,

I'm sorry for the delay.

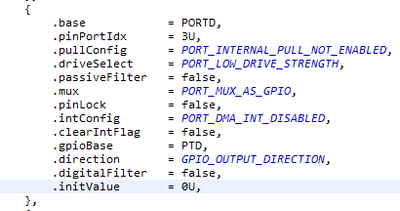

Please find the test project attached (S32DS 3.4, SDK RTM 4.0.3)

The slave receives 4 8bit frames in the AUTOPCS mode (1MHz).

Regards,

Daniel