- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K146 FTM trouble

S32K146 FTM trouble

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K146 FTM trouble

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

I'm working with S32K146 controller and having trouble with FTM4.

I'm initialize the timer in counter mode and after start CNT register change value from 0 to 65535 in a circle.

Now I want to configure interrupt when CNT register change value from 65535 to 0.

I set TOIE bit in SC register

FTM4->SC |= FTM_SC_TOIE_MASK;

and set interrupt enable in NVIC

S32_NVIC->ISER[FTM4_Ovf_Reload_IRQn / 32] |= (1 << (FTM4_Ovf_Reload_IRQn % 32));

I also add interrupt handler function:

void FTM4_Ovf_Reload_IRQHandler(void)

{

FTM4->SC &= ~FTM_SC_TOF_MASK;

return;

}

Vector Table in startup file have corresponding pointer to my handler

.long FTM4_Ovf_Reload_IRQHandler /* FTM4 Counter overflow and Reload interrupt*/

But, CNT register overflow triggered DefaultISR handler.

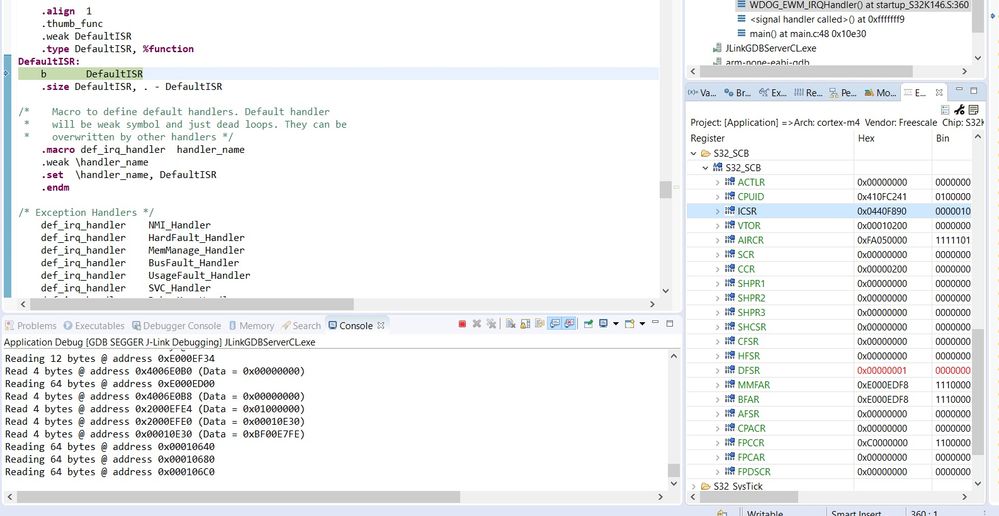

I stop debugger and see programm stay in DefaultISR function located at 0x1065c in code memory.

At this time register xPSR = 0x21000090. FTM4_Ovf_Reload_IRQHandler located at 0x0134ad. Vector table offset VTOR = 0x10200. Code memory 0x10440 (corresponding to the interrupt vector 0x90) store word 0x1034AD.

The most intresting, when I change in my code FTM4 to FTM0 or FTM1 the trouble goes away

FTM0 or FTM1 worked nice!

FTM2-FTM5 dotn work.

Why? Help me!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Oleg,

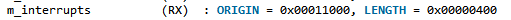

I don't know why yet, but it works when the vector table is moved to, for example:

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

I changed vector table location to 0x11000 and trouble goes away too.

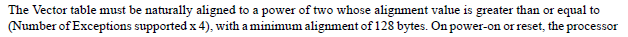

What alignment should be VTOR?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Oleg,

Yes, it must be aligned.

Please take a look at ARMv7-M Architecture Reference Manual

https://developer.arm.com/docs/ddi0403/e/armv7-m-architecture-reference-manual

B1.5.3 The vector table

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Oleg,

I don't see any issue in the description.

Can you share the project?

What is the value of S32_SCB_ICSR and S32_SCB_CFSR?

BR, Daniel