- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

S32K116 UART Communication protocol emulation over FLEXIO

I'm trying to emulate UART over flexi on the S32116EVB developer kit. I want to keep the TX of UART by default high (open drain) and then start putting data on tx line. As explained in the reference manual I have the following bits in the register to make it supprort opendrain.

FLEXIO-> SHIFTCTL [0] | = FLEXIO_SHIFTCTL_PINCFG (0x01);

FLEXIO-> SHIFTCTL [0] | = FLEXIO_SHIFTCTL_PINPOL (0x01);

When I do the setting as mentioned above in the register , TX line remains at low state and no communication happens (failed to transmit)

I want to set the state of the pin to default high. and start transmission over tx line, Currently this is not possible without external pull up resistor.

So can anyone tell me, if it is true that I always need an external pullup register to achieve communication as given in the above picture?

I am attaching my sample setting too for tx line

clock enable

PCC-> PCCn [PCC_PORTA_INDEX] | = 1 << PCC_PCCn_CGC_SHIFT;

// PORTD_0 set as FLEXIO

PORTD-> PCR [2] | = 0x00000400; / * Port D2: MUX = FLEXIO * /

// Enable clock to the FXIO

(PCC-> PCCn [PCC_FlexIO_INDEX]) | = 0x41000000;

FLEXIO-> CTRL | = FLEXIO_CTRL_DBGE (1);

FLEXIO-> SHIFTSTAT = 0x0F;

// TRANSMITTER

// shifter configuration

FLEXIO-> SHIFTCTL [0] | = (FLEXIO_SHIFTCTL_TIMSEL (0) | FLEXIO_SHIFTCTL_TIMPOL (0) | FLEXIO_SHIFTCTL_PINSEL (0x03) | FLEXIO_SHIFTCTL_SMOD (0x02));

FLEXIO-> SHIFTCTL [0] | = FLEXIO_SHIFTCTL_PINCFG (0x01);

FLEXIO-> SHIFTCTL [0] | = FLEXIO_SHIFTCTL_PINPOL (0x01);

FLEXIO-> SHIFTCFG [0] | = (FLEXIO_SHIFTCFG_INSRC (0) | FLEXIO_SHIFTCFG_SSTOP (0x03) | FLEXIO_SHIFTCFG_SSTART (0x02));

// set baud rate

// FLEXIO-> TIMCMP [0] = 0x00000F04;

// timer configuration

FLEXIO-> TIMCFG [0] | = (FLEXIO_TIMCFG_TIMOUT (0) | FLEXIO_TIMCFG_TIMDEC (0) | FLEXIO_TIMCFG_TIMDIS (0x02) | FLEXIO_TIMCFG_TIMENA (0x02) | FLEXIO_TIMCFG_TSTOP (0x02) | FLEXIO_TIMCFG_TSTART (0x01));

Hi Jayashree pasane

PINCFG and PINPOL are for the logical behaves of the pin, but as long as you are using this pin as open drain, it will need a pull up to work. You can use the internall pullup of the MCU, it is enabled with the PE and PS of the PORT_PCRn field.

Hope this helps

Best regards

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

-------------------------------------------------------------------------------

Hello Jorge,

Thank you again for the response.

I tried to enable the internal pull up, but still I face the same issue. I am trying to use Evaluation board S32K116EVB.

Regards,

Jayashree P

Hi jayashree pasane

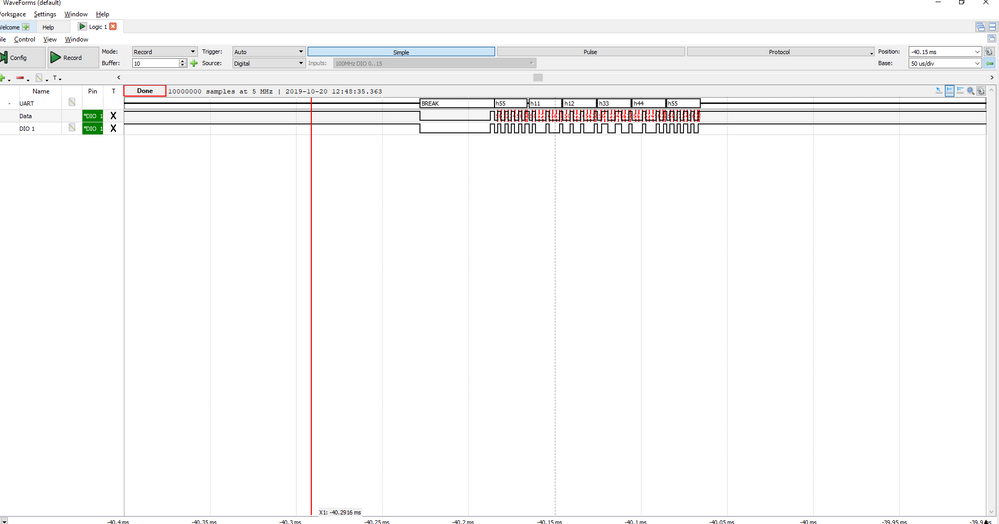

In order to have the flexIO TX of UART by default high you need to set:

FLEXIO-> SHIFTCTL [0] | = FLEXIO_SHIFTCTL_PINCFG (0x00);

FLEXIO-> SHIFTCTL [0] | = FLEXIO_SHIFTCTL_PINPOL (0x03);

With this config, you will have TX high by default and when transmission happens, it will act as your second scope.

Regards

Jorge Alcala