- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K VLPS mode entry and exit

S32K VLPS mode entry and exit

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K VLPS mode entry and exit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

I have followed the Power management AN5425 pdf provided by Nxp for Power mode and exit s32k116.

I have done for RUN to VLPS mode entry and tested the current consumption it is 4mA, But as per datasheet, it should be less than 1mA. So how to further reduce the current consumption by the controller?

And also how to disable the clock monitors?

And if possible also let me know how to come to normal RUN mode through CAN using pretended network mode.

Please let me know.

void RUN_to_VLPS (void)

{

/* Adjust SCG settings to meet maximum frequencies value */

scg_disable_pll_and_firc();

/* Enable SLEEPDEEP bit in the Core

* (Allow deep sleep modes) */

S32_SCB ->SCR|=FSL_SCB_SCR_SLEEPDEEP_MASK;

/* Allow very low power run mode */

SMC->PMPROT |= SMC_PMPROT_AVLP_MASK;

/* Select VLPS Mode */

SMC->PMCTRL=SMC_PMCTRL_STOPM(0b10);

PMC->REGSC |= PMC_REGSC_BIASEN_MASK;

/* Check if current mode is RUN mode */

if(SMC->PMSTAT == 0x01)

{

/* Go to deep sleep mode */

asm("WFI");

}

}

Regards,

Shinde Umesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shinde Umesh,

Recently,in VLPS mode, I also encountered the same problem. How did you solve it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Mr. Daniel,

I have made one file to enter VLPS mode and to come back from it through Pin Interrupt, I referred to the project sent by you previously.

Please let me whether any modification is required in wakeup and sleep functionality.

I am asking these questions because first time I am designing this functionality for the project.

#include "S32K116.h"

void init_NVIC(void);

void PORTE_IRQHandler(void);

void RUN_to_VLPS(void);

#define SWMAX_VALUE 5000

extern uint16_t Cntr;

volatile uint8_t vlps = 1;

volatile uint8_t sleep_mode_cmd = 0;

void Mode_Change(void)

{

init_NVIC();

PORTE->PCR[5] = 0x00008000; // Lock the Port Pin PTE5

PORTE->PCR[5] = PORT_PCR_IRQC(9); // Enable Interrupt on Rising-Edge

if((Cntr >= SWMAX_VALUE)) /*Enter to VLPS mode*/

{

//CAN_Wakeup_Config();

RUN_to_VLPS();

}

if(((CAN0->WU_MTC >> CAN_WU_MTC_WUMF_SHIFT)&CAN_WU_MTC_WUMF_WIDTH) == 1u)

{

CAN0->WU_MTC = CAN_WU_MTC_WUMF(1); // Clear the wakeup bit after successful wakeup

}

}

#if 1

void RUN_to_VLPS(void)

{

/* Disable the JTAG port pins */

/* Disable Adc Pins */

PMC->REGSC |= PMC_REGSC_BIASEN(1); // [1] CLKBIASDIS = 1 In VLPS mode, the bias current for SIRC, FIRC, PLL is disabled

/* Disable the Fosc and Sosc from chip*/

SCG->FIRCCSR = SCG_FIRCCSR_FIRCEN(0);

while(SCG->FIRCCSR & (1 << 24));

SCG->SOSCCSR = SCG_SOSCCSR_SOSCEN(0);

S32_SCB->SCR |= S32_SCB_SCR_SLEEPDEEP_MASK|0x2; /* allow deep sleep mode0 */

SMC->PMPROT = SMC_PMPROT_AVLP(1); /* allow very low power mode*/

SMC->PMCTRL = SMC_PMCTRL_STOPM(2);

if(SMC->PMSTAT == 0x01)

{

asm("WFI");

}

}

#if 0

void CAN_Wakeup_Config(void)

{

/* freez mode enter sequence */

CAN0->MCR = CAN_MCR_FRZ(1); // Enter to Freez mode to set dependent Registers

CAN0->MCR = CAN_MCR_HALT(1); // set the HLT bit to enter in freez mode

if( ((CAN0->MCR) >> CAN_MCR_MDIS_SHIFT)&CAN_MCR_MDIS_WIDTH) == 1u )

{

CAN0->MCR = CAN_MCR_MDIS(0); // clear module disable bit

}

if(((CAN0->MCR >> CAN_MCR_FRZACK_SHIFT )&CAN_MCR_FRZACK_WIDTH) == 1u)

{

CAN0->MCR = CAN_MCR_PNET_EN(1); // FRZ mode only

CAN0->FLT_ID1 = CAN_FLT_ID1_FLT_ID1(0x18FEF519); // FRZ mode only

CAN0->FLT_ID2_IDMASK = CAN_FLT_ID2_IDMASK_IDE_MSK(1); // FRZ mode only

CAN0->FLT_ID2_IDMASK = CAN_FLT_ID2_IDMASK_FLT_ID2_IDMASK(0x14FF05E8); // FRZ mode only

}

CAN0->MCR = CAN_MCR_FRZ(0); // Exit from freez mode

CAN0->MCR = CAN_MCR_HALT(0); // Clear the HLT bit to exit in freez mode

/* CAN Pretended Network mode configuration */

CAN0->IMASK1= CAN_IMASK1_BUF31TO0M(0xffff); // Allow MB 0_15 for INTR generation

CAN0->CTRL1_PN = CAN_CTRL1_PN_WUMF_MSK(1); // wakeup by match flag

CAN0->CTRL1_PN = CAN_CTRL1_PN_NMATCH(1); // filter criteria must match once

CAN0->CTRL1_PN = CAN_CTRL1_PN_IDFS(1); // greater than or equal to targer value

CAN0->CTRL1_PN = CAN_CTRL1_PN_FCS(0); // Msg ID filter only

CAN0->FLT_ID1 = CAN_FLT_ID1_FLT_IDE(1); // Extended CAN messages

}

#endif

void init_NVIC(void)

{

// PORTE_interrupt

S32_NVIC->ICPR[1] = (1 << (61 % 32));

S32_NVIC->ISER[1] = (1 << (61 % 32));

S32_NVIC->IPR[63] = 0x10; // Priority level 1

}

void PORTE_IRQHandler(void)

{

PORTE->PCR[5] |= (1 << 24); // [24] ISF = 1 Clear the interrupt flag

PORTE->DFER |= (1 << 5); // Digital filter is enabled on the PTC12 pin

if(vlps)

{

vlps = 0; // VLPS mode

S32_SCB->SCR = 0x04;

// [4] SEVONPEND = 0 only enabled interrupts can wakeup

// [2] SLEEPDEEP = 1 deep sleep

// [1] SLEEPONEXIT = 0 do not enter deep sleep on return from an ISR

(void)S32_SCB->SCR; // make sure it is written before it leaves the ISR

}

else

{

vlps = 1;

}

}

Thanks and regards,

Shinde Umesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shinde Umesh,

I have found a few issues.

- PTE5 is the CAN0_TX pin not the RX pin.

- The PORTE interrupt ID is not 63 but 9 on S32K11x.

- The code disables the FIRC and SOSC clocks, but the first, the SIRC clock must be the system clock.

- Once the MCU is back in the RUN mode, I guess, you want to re-enable the previous clock configuration (application-dependent).

- The CAN_WU_MTC_WUMF flag won’t be set since the wake-up source is the PORTE interrupt.

- Why do you enable the PTE5 filter in the PORTE handler? This should be done before the interrupt is enabled.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Mr. Daniel,

I saw in code sent that the filter needs to enable for detecting the interrupt that's why I have enabled it.

Is it not required to enable the filter for the port pin to detect interrupt?

And about CAN_WU_MTC_WUMF bit of MCR is set whenever the message received after filtration, I have read this in Reference manual of S32k.

Can you please tell me whether I have configured register for CAN wakeup in the right manner or not?

If not can you please tell me how to enable CAN wakeup for 0x123456 this example ID in s32k116?

Thanks&Regards,

Shinde Umesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shinde Umesh,

The filter is not requires, I was just wondering why you enabled that feature in the handler, it should be enabled before the interrupt triggers.

As I already mention, in VLPS, the FlexCAN cannot be a wake up source.

The port interrupt can be used and once the MCU is in RUN mode again, you can enable the FlexCAN module, the first message will be lost of course.

You can use the PN mode, but it works in STOP1/2 only.

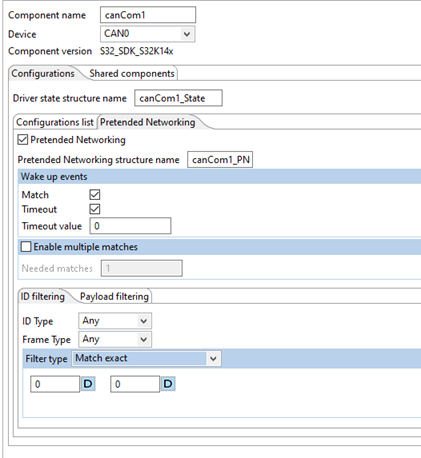

Please use the FlexCAN SDK driver and Processor expert to configure the PN mode.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Mr. Daniel,

Thanks for your response and suggestions.

Regards,

Shinde Umesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Mr. Daniel Martynek,

As given example by you, in this, you are using RTC along with Port INTERRUPT as I understood. But in my case, I just want that if any button is pressed or any CAN message is arrived then it should come back to the normal RUN mode from VLPS mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello shindeu66@gmail.com,

Please disconnect the debugger and power-cycle the MCU, otherwise, the MCU enters an emulated Stop mode instead.

All GPIOs retain their state in Stop modes, make sure you are not driving any external load.

Do you have an EVB or your own board? Where do you measure the current?

There are a few examples you can refer to:

power_mode_switch_s32k116 SDK example in the S32 design studio

https://community.nxp.com/docs/DOC-341788

There are two clock monitors on S32K11x:

The SOSC clock monitor: Section 28.1.4 System clock and clock monitor requirement

CMU FIRC monitors: Section 30.1 CMU chip-specific information

Please ensure that CMU is gated by its PCC.CGC before entering any Stop mode.

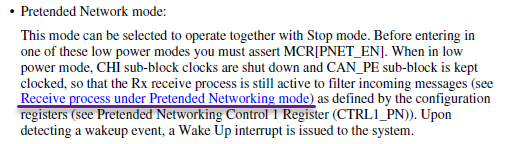

The pretended network mode can be used in STOP1/2 but not in VLPS.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you please tell me, How to get back in Normal RUN from STOP mode using CAN pretended network mode and Pin interrupt ?

Regards,

Shinde Umesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello shindeu66@gmail.com,

There is no Pretending mode wake-up example available.

But the FlexCAN SDK driver supports it:

The Example S32K144 RTC VLPS S32DS.R1 is using a Pin interrupt as a wake-up source, for instance.

You don’t need to reconfigure the CAN_RX pin to GPIO as the pin interrupt works in all the digital functions of a pin.

Just enable this interrupt (PORTx_PCRn) before the MCU enters VLPS.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Mr. Daniel Martynek,

In my current project, my lead is not using FlexCan Component from the S32 studio. He is configured CAN through the Vector Geny tool.

How I will configure then this PN mode ?.

and one more question sir,

who is the caller of this function how decided PORTC_IRQHandler?

Regards,

Shinde Umesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shinde Umesh,

Unfortunately, I don’t have any experience with the Vector Geny tool.

I would recommend that you to go through the Vector documentation or to contact Vector.

The PNET mode is explained in the S32K1xx RM though.

I’m not sure if I understand what you mean.

The PORTC_IRQHandler is called when a PORTC interrupt is detected by the PORT module and requested to the Core NVIC. So, the interrupt must be enabled in the PORTC module and NVIC.

There is one interrupt for the whole PORTC, the handler must read either PORT_ISFR or PORT_PCRn to determine the source of the interrupt and clear the interrupt flag.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mr.Daniel

Recently,I also have some problems on RUN and VLSP mode configuration, before you answer, I am the following information is correct:

1. S32K144 chips do not have CAN RXD wake function module

2. Before enter VLSP mode, need to configure the RTC CLOCK module

and The following is my adopted the SDK software configuration module:

static void gpio_port_int_init(void)

{

INT_SYS_EnableIRQ(PORTB_IRQn);

INT_SYS_InstallHandler(PORTB_IRQn, &gpio_portb_irq, (isr_t *)0);

INT_SYS_EnableIRQ(PORTD_IRQn);

INT_SYS_InstallHandler(PORTD_IRQn, &gpio_portd_irq, (isr_t *)0);

INT_SYS_EnableIRQ(PORTE_IRQn);

INT_SYS_InstallHandler(PORTE_IRQn, &gpio_porte_irq, (isr_t *)0);

PINS_DRV_SetPinIntSel(GPIO_CP_UNLOCK_PORT,GPIO_CP_UNLOCK_PIN,PORT_DMA_INT_DISABLED);

PINS_DRV_SetPinIntSel(GPIO_CP_WAKE_PORT,GPIO_CP_WAKE_PIN,PORT_DMA_INT_DISABLED);

PINS_DRV_SetPinIntSel(GPIO_CC_WAKE_PORT,GPIO_CC_WAKE_PIN,PORT_DMA_INT_DISABLED);

PINS_DRV_SetPinIntSel(GPIO_VCU_WAKE_PORT,GPIO_VCU_WAKE_PIN,PORT_DMA_INT_DISABLED);

}

void init_NVIC(void)

{

PINS_DRV_SetPinIntSel(PORTE,5U,PORT_INT_RISING_EDGE);

}

void Power_RUN_to_STOP (void)

{

PMC->REGSC |= PMC_REGSC_BIASEN(1); // [1] CLKBIASDIS = 1 In VLPS mode, the bias current for SIRC, FIRC, PLL is disabled

/* Disable the Fosc and Sosc from chip*/

SCG->FIRCCSR = SCG_FIRCCSR_FIRCEN(0);

while(SCG->FIRCCSR & (1 << 24));

SCG->SOSCCSR = SCG_SOSCCSR_SOSCEN(0);

S32_SCB->SCR |= S32_SCB_SCR_SLEEPDEEP_MASK|0x2; /* allow deep sleep mode0 */

SMC->PMPROT = SMC_PMPROT_AVLP(1); /* allow very low power mode*/

SMC->PMCTRL = SMC_PMCTRL_STOPM(2);

if(SMC->PMSTAT == 0x01)

{

asm("WFI");

}

}

void power_set_mode(POWER_SYS_TYPE mod)

{

if(mod == POWER_SYS_SLEEP)

{

init_NVIC();

//power_can_wakeup_set();

Power_RUN_to_STOP();

}

}

Regards,

Katrinal