- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: Problem of the CAN sampling point test value being too small for S32K3

Problem of the CAN sampling point test value being too small for S32K3

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, NXP

When developing with S32K311, an external crystal oscillator of 16 MHz is selected. When configuring CANFD, the CAN clock source uses the AIPS_PLAT_CLK at 60 MHz. 80% sampling point is configured for the data field, and TDC is enabled. However, the actual measured sampling point in CANOE can only reach 72%.

This issue also occurs in tests on other models such as the S32K312 and S32K342.

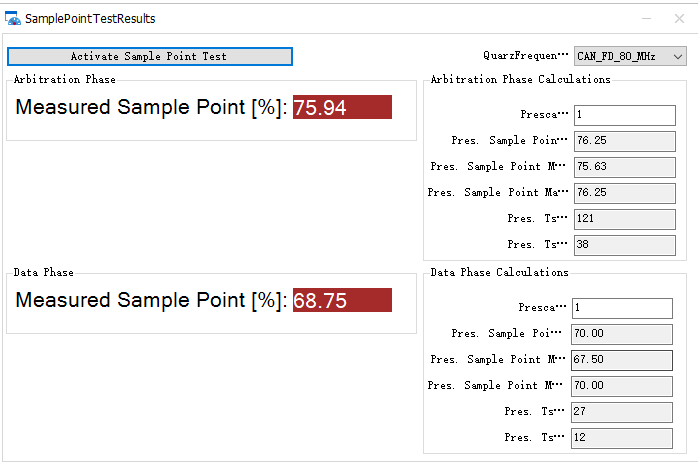

The following is one of our configurations where we set the sampling points and test data. We configured the sampling point to be 76%, but the actual test result was 67%.

Best Regards,

xianlong

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi@wuxianlong

I'm sorry, I cannot perform this test.

I do not have suitable interference equipment to conduct it, and the test results in the FLEXCAN report already prove that the test passed.

I can send you the relevant proof privately.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For CAN FD data phase the latest possible sample point must be set in CANoe. Then the VH6501 sends frames and lengthens the individual bits by one tick after each interval.

This seems to be a configuration issue with your VH6501. You can try modifying the parameters here to 70%, 76.667%, and 80% and then testing again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, @Senlent

We have modified multiple configurations. Under the condition that S32K3 is configured to 80%, the best result tested by CANoe is 72%

Best Regards,

xianlong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi@wuxianlong

Could you please share your project, i will take time to test it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,@Senlent

We consulted several experienced engineers. They described that there are also problems with the small sampling point test in S32K1 and K3, and this problem may not be strongly related to the MCU.However, the test results vary when different testing instruments are used. When using CANoe for testing, the test results are all on the low side. They suggest that the sampling point configured for S32K3 can be appropriately increased under the actual test requirement of 80%. You can use any NXP demo to conduct a test, and this phenomenon should be reproducible.

Best Regards,

xianlong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi@wuxianlong

This should still be a testing issue, not caused by the MCU.

However, I will spend some time doing some simple tests. I will probably use an oscilloscope to test directly, which should be the most accurate measurement method.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,@Senlent

If you have more convincing results, please share them with us as well.

We used some other instruments for testing, and the obtained sampling points are relatively close to what we expected in the settings. However, for customers, CANoe has a very high level of industry recognition.

Best Regards,

xianlong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi@wuxianlong

It's possible that the client's tests are flawed; please trust your own testing.

I will take some time to conduct a few tests, but this isn't a priority for me and may take a few

days to get back to you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi@wuxianlong

I'm sorry, I cannot perform this test.

I do not have suitable interference equipment to conduct it, and the test results in the FLEXCAN report already prove that the test passed.

I can send you the relevant proof privately.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content