- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

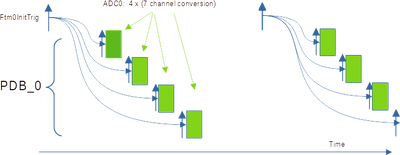

I want to generate multiple triggers for the ADC.

The PDB's input trigger originates from PWM:

Ftm0InitTrig -> Pdb0TrgIn. Relative to this, I want to generate ADC conversion on 600, 1300, 2000, and 2700 clock delays.

I can only make one trigger with (INST_PDB_0, 0, 0, delay) setup.

Did I misunderstand the PDB functions, or am I doing something wrong?

void PDB0_init(void)

{

PDB_DRV_Init(INST_PDB_0, &pdb_config_1_timerConfig0);

PDB_DRV_Init(INST_PDB_0, &pdb_config_1_timerConfig1);

PDB_DRV_Init(INST_PDB_0, &pdb_config_1_timerConfig2);

PDB_DRV_Init(INST_PDB_0, &pdb_config_1_timerConfig3);

PDB_DRV_Enable(INST_PDB_0); // enable PDB before LDOK

// config pretriggers on ch0 based on component setting

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig0);

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig1);

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig2);

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig3);

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig4);

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig5);

PDB_DRV_ConfigAdcPreTrigger(INST_PDB_0, 0UL, &pdb_config_1_adcTrigConfig6);

/* Set PDB0 modulus value */

PDB_DRV_SetTimerModulusValue(INST_PDB_0, 4096);

/* PDB0 pre-trigger0 delays set to sense in the middle of the PWM cycle */

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 0, 600); // 640 -> 16us, OK

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 1, 1300); // 1300 -> 24us ?

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 2, 2000); // 2400 -> 33.6us ?

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 3, 2700); // 2700 -> 42.4us ?

// PDB_DRV_SetCmpPulseOutDelayForHigh(INST_PDB_0, 0L , 0); // <- PDB0PulseOut signal in TRGMUX

// PDB_DRV_SetCmpPulseOutDelayForLow(INST_PDB_0, 0L, 600); // <- PDB0PulseOut signal in TRGMUX

// PDB_DRV_SetCmpPulseOutEnable(INST_PDB_0, 1<<0, true);

//PDB_DRV_SetValueForTimerInterrupt(INST_PDB_0, 4999); /* Set PDB1 interrupt delay value */

PDB_DRV_LoadValuesCmd(INST_PDB_0); /* Load PDB0 configuration */

}

已解决! 转到解答。

Hi,

if the green box represents single ADC channel then you can achieve this by setting individual pretriggers delay. If it represents multiple channels then it can be done by using back-2-back mode, but just 2 multiple conversion can be initiated using both PDB channels.

BR, Petr

Of these, only the first configuration is active with correct timing for any selected clock delay:

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 0, 600); // 640 -> 16us, OK

These are not triggering the ADC :

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 1, 1300); // 1300 -> 24us ?

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 2, 2000); // 2400 -> 33.6us ?

PDB_DRV_SetAdcPreTriggerDelayValue(INST_PDB_0, 0, 3, 2700); // 2700 -> 42.4us ?

I observed the ADC conversion in the ADC0_IRQHandler() using an output pin On/Off during the interrupt execution.

My setup for this:

---------------------------------------------------------------------------------

/*! @brief ADC pre-trigger configurations */

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig0 = {

.adcPreTriggerIdx = 0U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = false

};

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig1 = {

.adcPreTriggerIdx = 1U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = true

};

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig2 = {

.adcPreTriggerIdx = 2U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = true

};

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig3 = {

.adcPreTriggerIdx = 3U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = true

};

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig4 = {

.adcPreTriggerIdx = 4U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = true

};

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig5 = {

.adcPreTriggerIdx = 5U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = true

};

const pdb_adc_pretrigger_config_t pdb_config_1_adcTrigConfig6 = {

.adcPreTriggerIdx = 6U,

.preTriggerEnable = true,

.preTriggerOutputEnable = true,

.preTriggerBackToBackEnable = true

};

/*! @brief PDB timer configurations */

const pdb_timer_config_t pdb_config_1_timerConfig0 = {

.loadValueMode = PDB_LOAD_VAL_IMMEDIATELY,

.seqErrIntEnable = false,

.clkPreDiv = PDB_CLK_PREDIV_BY_1,

.clkPreMultFactor = PDB_CLK_PREMULT_FACT_AS_1,

.triggerInput = PDB_TRIGGER_IN0,

.continuousModeEnable = false,

.dmaEnable = false,

.intEnable = false,

.instanceBackToBackEnable = false,

};

const pdb_timer_config_t pdb_config_1_timerConfig1 = {

.loadValueMode = PDB_LOAD_VAL_IMMEDIATELY,

.seqErrIntEnable = false,

.clkPreDiv = PDB_CLK_PREDIV_BY_1,

.clkPreMultFactor = PDB_CLK_PREMULT_FACT_AS_1,

.triggerInput = PDB_TRIGGER_IN0,

.continuousModeEnable = false,

.dmaEnable = false,

.intEnable = false,

.instanceBackToBackEnable = false,

};

const pdb_timer_config_t pdb_config_1_timerConfig2 = {

.loadValueMode = PDB_LOAD_VAL_IMMEDIATELY,

.seqErrIntEnable = false,

.clkPreDiv = PDB_CLK_PREDIV_BY_1,

.clkPreMultFactor = PDB_CLK_PREMULT_FACT_AS_1,

.triggerInput = PDB_TRIGGER_IN0,

.continuousModeEnable = false,

.dmaEnable = false,

.intEnable = false,

.instanceBackToBackEnable = false,

};

const pdb_timer_config_t pdb_config_1_timerConfig3 = {

.loadValueMode = PDB_LOAD_VAL_IMMEDIATELY,

.seqErrIntEnable = false,

.clkPreDiv = PDB_CLK_PREDIV_BY_1,

.clkPreMultFactor = PDB_CLK_PREMULT_FACT_AS_1,

.triggerInput = PDB_TRIGGER_IN0,

.continuousModeEnable = false,

.dmaEnable = false,

.intEnable = false,

.instanceBackToBackEnable = false,

};

Hi,

you have back-to-back enabled for pretriggers1-7, so its delay is ignored. So disable it thus pretrigger delay can be used

However with back-to-back operation a conversion should be done too.

BR, Petr

Hello Petr,

I don't understand your response.

Is the S32K144's PDB hardware support multiple delayed triggers, as the image depicts, or not?

If yes, and you know the solution can you share it with us?

Best Regards,

Antal

Hi,

if the green box represents single ADC channel then you can achieve this by setting individual pretriggers delay. If it represents multiple channels then it can be done by using back-2-back mode, but just 2 multiple conversion can be initiated using both PDB channels.

BR, Petr

hello @PetrS

I got the same error.

I want to modify the S32K144 pmsm demo to add more analog signals. The original demo uses adc0 to get 1 analog signal, and adc1 to get 2 analog signals. I want to use adc0 and adc1 to get 3 analog signals respectively, totally 6 analog signals. And the pretrigger delay time is 0, 200, 2000. Please see my thread for detail. Also the project.

https://community.nxp.com/t5/S32-SDK/how-to-config-adc-and-pdb-for-multiple-channels/m-p/1549325

But I got pdb sequency error during debug phase and have no idea on how to solve it. Could you give me some support?

Hi,

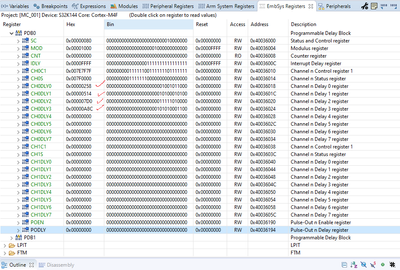

usage of functions PDB_DRV_ConfigAdcPreTrigger, PDB_DRV_SetAdcPreTriggerDelayValue is correct.

So you do not see ch0DLYn registers written, and triggers does not happen in desired time?

Do you have pdb_config_1_adcTrigConfign defined with pretrigger index and pretrigger output options enabled?

BR, Petr