- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- IAR memory window not change after flash program

IAR memory window not change after flash program

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IAR memory window not change after flash program

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

p:S32K146

IAR:9.30.1

In the OTA progress, after erase ,the data at the which address is 0x20000 all become 0xff,but after program like 8 bytes for one time , the data at the 0x20000 looked at the memory window of IAR is still 0xff,but after 128 or 256 bytes later, the data is the expected data programmed.However ,at the end of the OTA, when tried to read the flash back by the link,the ata is the same with the file downloaded by the can.

below is the memory window of the IAR

below is the flash code example:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @qimao-marvin,

It’s possible that the issue is due to either: The IDE memory view not being refreshed, or the effect of cache or the prefetch buffer.

Is the cache enabled?

If so, it might be affecting what you see in memory.

Prefetch buffer is enabled by default. You can disable it (from SRAM) using the following configuration:

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM1(0x3u);

MSCM->OCMDR[1u] |= MSCM_OCMDR_OCM1(0x3u);

Try reading the memory directly from the core and compare it with the flash content to verify consistency.

In our department, we don’t use the IDE, so we can’t confirm its behavior.

If the issue persists, it might be worth contacting IAR support to check whether the memory view needs to be manually refreshed.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

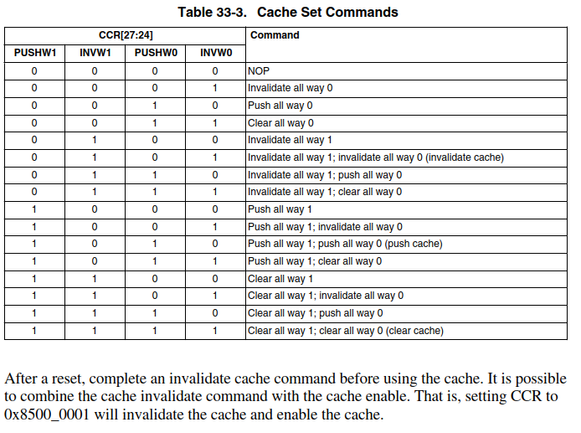

In the init function of falsh ,the register PCCCR will be set

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @qimao-marvin,

Yes, but there’s also the prefetch buffer—as I mentioned, this is a separate cache.

However, it’s only a 128-bit buffer and can be updated simply by reading data from a different location.

Regards,

Daniel