- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

FlexioLIN Baudrate(S32K344 )

Hi NXP team,

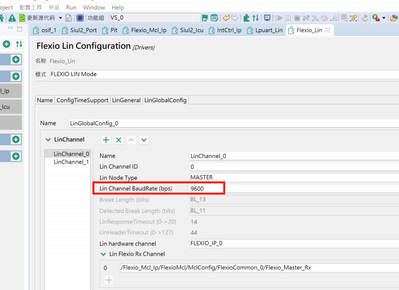

We develop S32K344 with RTD2.0.0 now, but we meet some problem for FlexioLIN. We try Lin_Ip_FrameTransfer_S32K344 example and test flexio LIN as below setting(baudrate 9600), but our receiver(toomoss) can't receive any data. If we set baudrate 19200 in our receiver(toomoss), it can receive data normally. The baudrate is always twice as large than S32DS setting. There is no issue for UartLin, only FlexioLin have this issue, please help to check it. Thanks.

Wade

Hi JAY_SUN1,

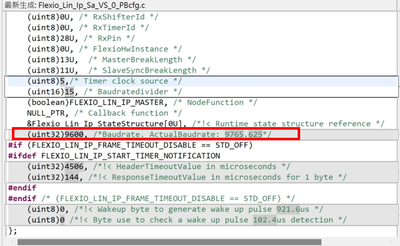

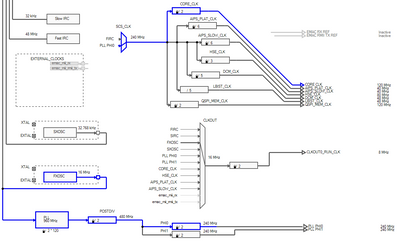

I ran the example with both baudrate = 9600 (ActualBaudrate = 9765) and 19200 successfully. In this situation: CORE_CLK = 160MHZ is the clock source of FlexIO_CLK. Perhaps, your board can't run with baudrate = 9600 (because ActualBaudrate = 9765 - baudrate deviation too high).

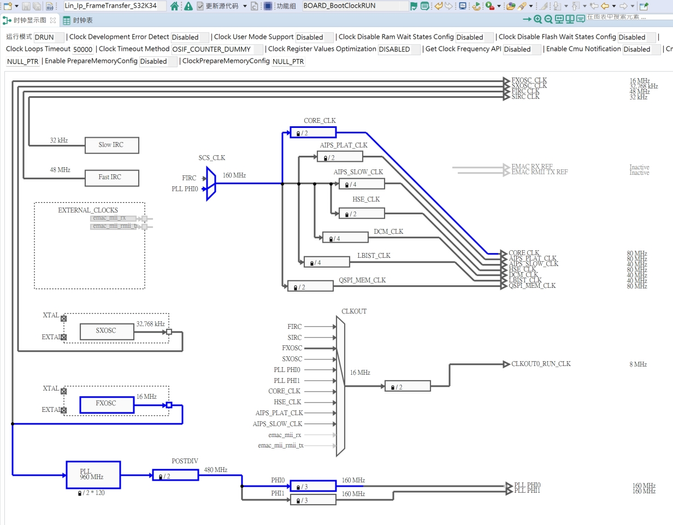

To decrease baudrate deviation, I decreased CORE_CLK = 120MHZ and select baudrate = 9600 then ActualBaudrate = 9615 (Baudrate deviation has decreased very much). I ran this clock configuration with example and it is OK with both baudrate = 9600 and 19200.

Could you try to run the example with my clock configuration and let me know the result?

Best regards,

Dan

Hi Dan,

I had tried your clock setting, but it's still not workable.

Then I try to let core clock to 80Mhz as below picture, and baudrate is correct, but I don't know why it can be normal.

You can see actual baudrate deviation has decreased very much as well. But it can commuciation normally.