- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: FlexCAN and FPROPSEG

FlexCAN and FPROPSEG

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FlexCAN and FPROPSEG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

In RM for S32K1xx (Rev. 9 but also in earlier versions) one can see that for Propagate Segment time in CTRL1 the register value should be written one less than the actual value i.e.

Propagation segment time = (PROPSEG + 1) × time-quanta

The same relates to CBT register i.e.

Propagation Segment Time = (EPROPSEG + 1) × Time-Quanta

While for the data part i.e. FDCBT register the propagation time has no +1. That is:

Propagation Segment Time = FPROPSEG × Time-Quanta

Could someone from NXP confirm that there is no typo in the manual?

2. Also another question regarding the baud rate.

When working with the can_pal example for S32K144 and playing with different baud rates in the CAN configuration window the following strange behavior is present: when FD is enabled and CAN PE clock source is selected to be the 80 MHz peripheral clock one cannot get registers values for e.g. 10 kbps for the Arbitration phase. The inserted 10 kbps is just reset to some higher values, although one would assume that in FD mode it should be possible to get 10 kbps by setting the Prescaler Devision Factor to let's say 799?

3. Yet another baud rate question.

There are a few documents like AN1798 which explains how to calculate the baud rate parameters to get the best tolerance. With highest tolerance in mind one usually gets somewhat lower percentage of the sampling point (varies from 60 to 80 %). This is different from the default values 87.25 (or so) shown in the baud rate configuration window of S32 Dev Studio. Also the RJW calculated by the manual like AN1798 is usually around 3 while the configuration windows shows normally the value of 1. The question is whether one should rely on the highest tolerance when calculating the best baud rate register values (and disregard the sampling point position) and which RJW value is preferred and why do they mismatch between the S32 Dev. Studio and the mentioned manual?

Thanks a lot in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1) the RM is correct here.

2) seems the PE’s FlexCAN component checks the given values against CTRL1 register still even if the FD is enabled and CBT should be used.

You can use below functions in your code to set desired bitrate for both the arbitration and data phase:

FLEXCAN_DRV_SetBitrate(base, &bitrate); // set arbitration bitrate

FLEXCAN_DRV_SetBitrateCbt(base, &bitrateFD); // set data bitrate

3)

RJW sets the MAXIMUM "slide" of the Bit-time that can be applied during a re-sync event. Also it affects calculation of required oscillator tolerance and so it can be advisable to use as high as possible value. RJW can be chosen as smaller of possible programmed value and PSEG2.

You should select a bit timing which fulfill max oscillator tolerance of device on CAN bus.

You can try to use the tool posted here https://community.nxp.com/docs/DOC-342618 for CAN bit timing calculation and see if it gives setting closed to your needs.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot for the clarification.

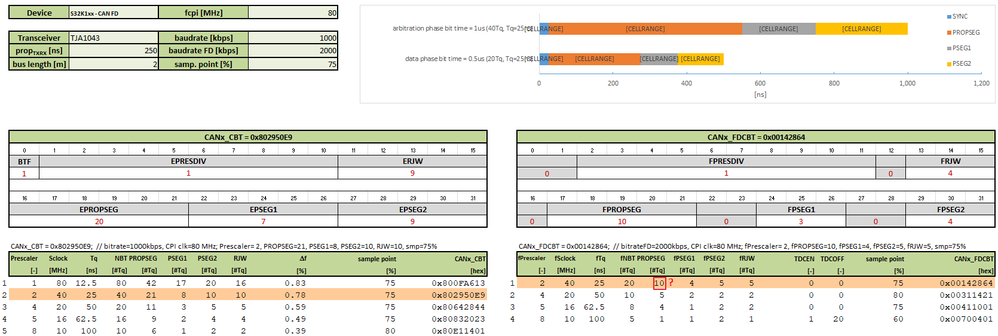

I played a bit with your Excel calculator and there is one thing which I do not understand. Please see the small red box with the question mark in the attached figure under the PROPSEG column on the right side.

As the snapshot shows for the data phase at baud rate 2000 kbps one see PROPSEG = 10. Could you please explain how this value is obtained? According to documentation the PROPSEG value should be calculated as follows:

t_prop_seg = 2 * (2 * 5 + 250) = 520*10^-9 # where 2 * 5 is the 2 meter x 5 ns (typical value)

PROPSEG = ROUND_UP( 520*10^-9 * Sclock ) = ROUND_UP( 520*10^-9 * 40 MHz) = 21

Following the above calculation the PROPSEG goes beyond the NBT which cannot be, so it should be definitely be lower than 20. So the question is how should one get around this problem and how does the Excel calculator come up with the value of 10?

Another small question in your reply you wrote:

RJW can be chosen as smaller of possible programmed value and PSEG2.

Do you mean PSEG1 instead of PSEG2?

Thanks a lot again for your help in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

during data phase only one node transmits dominant bits and so it is not needed to consider signal propagation time between nodes. Thus I used just propagation delay (TX-RX) of single transceiver in a calculation. Result is aprox half of PROPSEG calculated in nominal phase.

During resynchronization, either PSEG1 is lengthened or PSEG2 is shortened by certain number of tq. RJW sets maximum possible slide. So I assumed RJW cannot be higher then PSEG2.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot. It is clear now.

Could you please clarify the last question: Why do PSEG1 and PSEG2 in the calculator shown in the above snapshot differ? The documentation recipe for PSEG1 and PSEG2 is as follows:

1. reminder = NBT - 1 - PROP_SEG = 20 - 1 - 10 = 9

2. if reminder is odd (in this case it is) increment the PROP_SEG and recalculate the reminder which will give:

reminder = 20 - 1 - 11 = 8

PSEG1 = PSEG2 = reminder / 2 = 4

Apparently you prefer to keep PREP_SEG intact and increment PSEG2. What is the reason behind that and should this be a preferred recipe instead of what is written in the documentation?

Thanks a lot again for all your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

there is no necessity to have PSEG1 egual PSEG2 although it is mentioned in many guides, I think. This gives more options to set a desired sample point if PROPSEG is kept intact as you wrote. This is used in calculator too.

BR, Petr