- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Failure of LPSPI1 Slave, Where PTD.3 was as #PCS, on EVB S32K118 48pins

Failure of LPSPI1 Slave, Where PTD.3 was as #PCS, on EVB S32K118 48pins

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm running an example of lpspi_transfer_s32k118, on EVB S32K118 48pins, however this pair of LPSPI0 as master and LPSPI1 as slave are working failed.

The failure of major syndrome is due to the LPSI1 PCS0 where is working abnormally.

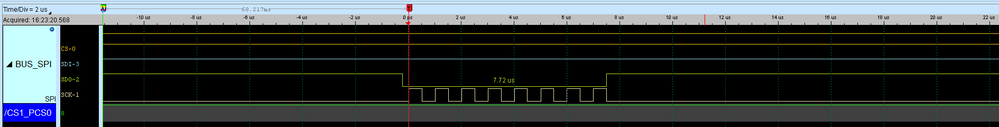

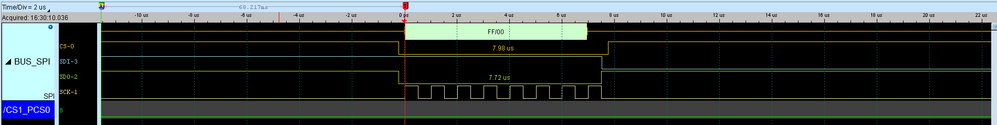

The waveforms are shown as the below.

LPSPI0 PCS1 was connecting to LPSPI1 PCS0. Obviously, the PCS0 was latched as high always during PCS1 drove.

LPSPI0 PCS1 was disconnecting to LPSPI1 PCS0. Obviously, the PCS1 was working normally.

IDE:

S32 Design Studio for S32 Platform

Version: 3.4

Build id: 201217 (Update 1)

SDK:

S32SDK_S32K1XX_RTM_4.0.2

EVB:

S32K118EVB2-0048

LPSPI0 configuration:

const lpspi_master_config_t lpspi_0_MasterConfig0 = {

.bitsPerSec = 1000000UL,

.whichPcs = LPSPI_PCS1,

.pcsPolarity = LPSPI_ACTIVE_LOW,

.isPcsContinuous = false,

.bitcount = 8U,

.lpspiSrcClk = 8000000UL,

.clkPhase = LPSPI_CLOCK_PHASE_1ST_EDGE,

.clkPolarity = LPSPI_SCK_ACTIVE_HIGH,

.lsbFirst = false,

.transferType = LPSPI_USING_INTERRUPTS,

.rxDMAChannel = 0U,

.txDMAChannel = 0U,

.callback = NULL,

.callbackParam = NULL

};

LPSPI1 configuration:

const lpspi_slave_config_t lpspi_1_SlaveConfig0 = {

.whichPcs = LPSPI_PCS0,

.pcsPolarity = LPSPI_ACTIVE_LOW,

.bitcount = 8U,

.clkPhase = LPSPI_CLOCK_PHASE_1ST_EDGE,

.clkPolarity = LPSPI_SCK_ACTIVE_HIGH,

.lsbFirst = false,

.transferType = LPSPI_USING_INTERRUPTS,

.rxDMAChannel = 0U,

.txDMAChannel = 0U,

.callback = NULL,

.callbackParam = NULL

};

BOARD_InitPins:

- options: {callFromInitBoot: 'true', coreID: core0}

- pin_list:

- {pin_num: '23', peripheral: LPSPI0, signal: sin, pin_signal: PTB3, direction: INPUT}

- {pin_num: '24', peripheral: LPSPI0, signal: 'sck, sck', pin_signal: PTB2, direction: OUTPUT}

- {pin_num: '14', peripheral: LPSPI0, signal: 'pcs, 1', pin_signal: PTB5, direction: OUTPUT}

- {pin_num: '15', peripheral: LPSPI0, signal: sout, pin_signal: PTB4, direction: OUTPUT}

- {pin_num: '1', peripheral: LPSPI1, signal: sin, pin_signal: PTD1, direction: INPUT}

- {pin_num: '2', peripheral: LPSPI1, signal: 'sck, sck', pin_signal: PTD0, direction: INPUT}

- {pin_num: '34', peripheral: LPSPI1, signal: sout, pin_signal: PTD2, direction: OUTPUT}

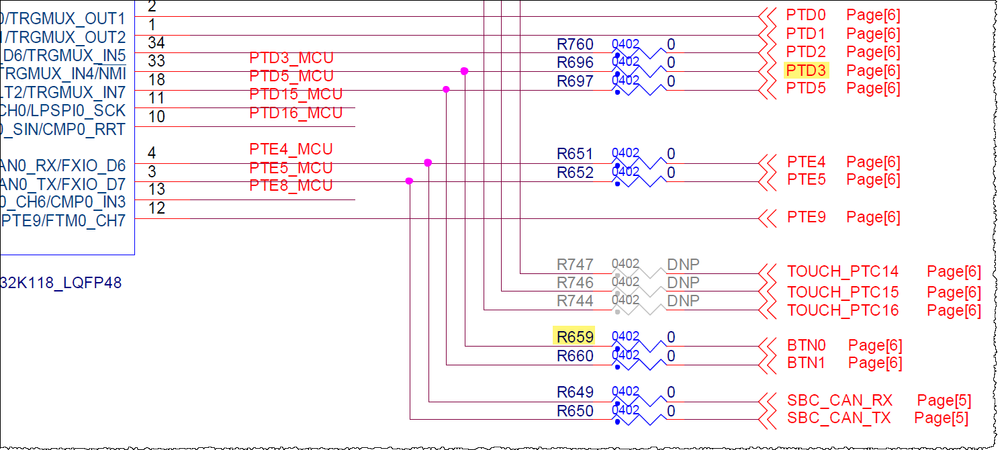

- {pin_num: '33', peripheral: LPSPI1, signal: 'pcs, 0', pin_signal: PTD3, direction: INPUT}

- {pin_num: '11', peripheral: FTM0, signal: 'ch, 0', pin_signal: PTD15, direction: OUTPUT}

- {pin_num: '29', peripheral: ADC0, signal: 'se, 3', pin_signal: PTA7}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

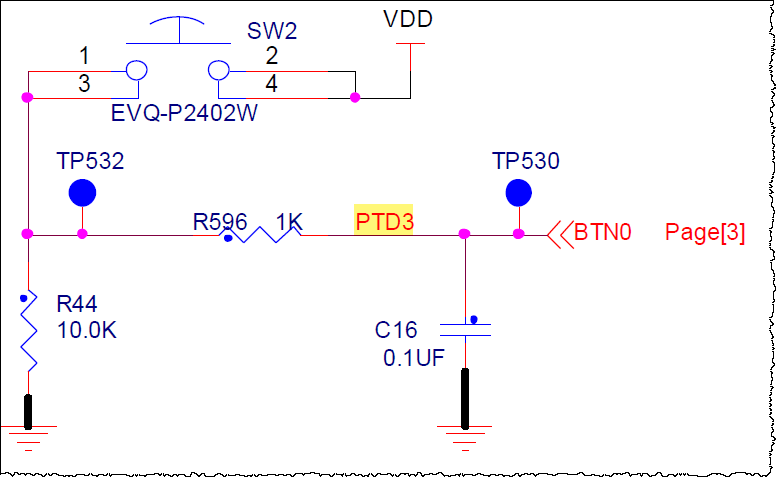

The PTD3 is connect to Push-Botton SW2 through R659 by default.

The NMI_b function is also enabled by default in FTFC_FOPT[NMI_PIN_CFG].

Can you change a PCS pin if possible.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

The PTD3 is connect to Push-Botton SW2 through R659 by default.

The NMI_b function is also enabled by default in FTFC_FOPT[NMI_PIN_CFG].

Can you change a PCS pin if possible.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------