- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

Hi,

I use S32K144 and st the clock as following with using SOSC:

SOSC : 8MHz, SPLL:160MHz, CORE_CLK: 80MHz, BUS_CLK: 40MHz; CLK_SRC_FIRC_DIV1:48MHz.

I select internal clock as input clock for FTM0 which is CLK_SRC_FIRC_DIV1 (48MHz), but when I run timer in normal counter and observe compare interrupt, it seems that timer work with 32MHz clock !!!

Next, I changed the CLK_SRC_FIRC_DIV1 to 2 and FTM works with correct frequency which is 24MHz !!!

FTM works fine with SOSC, SIRC, SPLL_DIV_2, SYS_CLK, LPO_CLK, but problem is when using FIRC as clock source for FTM with 48MHz configuration!!

has anybody any comment !

已解决! 转到解答。

Hi JeorgeB,

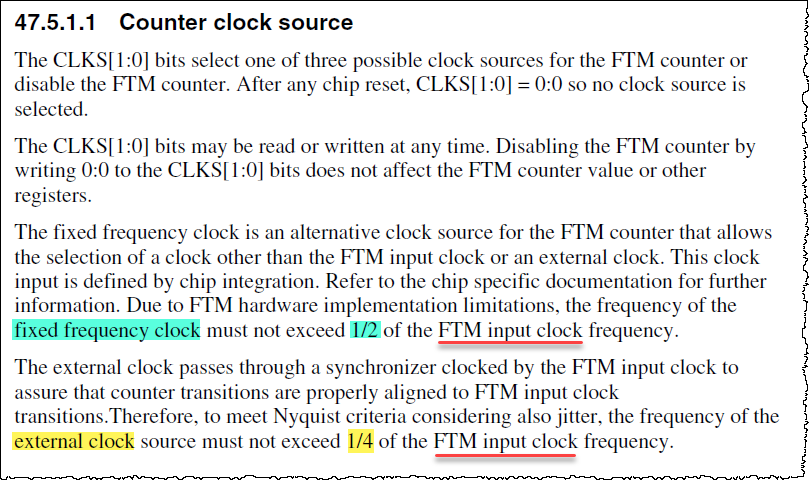

According to the description of "47.5.1.1 Counter clock source" and "Table 27-9. Peripheral module clocking":

The frequency of the fixed frequency clock(RTC_CLK) must not exceed 1/2 of the FTM input clock frequency(FTM System clock SYS_CLK)..

The frequency of the external clock source(TCLK0 \ TCLK1 \ TCLK2 \ SOSCDIV1_CLK \ SIRCDIV1_CLK \ FIRCDIV1_CLK \ SPLLDIV1_CLK) must not exceed 1/4 of the FTM input clock frequency(FTM System clock SYS_CLK).

Due to: SYS_CLK = CORE_CLK = 80MHz

So:

Frequency of external clock source should not exceed 20MHz.

Frequency of fixed clock source should not exceed 40MHz.

But it seems to conflict with your test results. Would you please attached your test project? So that I can test it faster.

Best Regards,

Robin

I test an alternative clock source which in FTM_CLOCK_SOURCE_FIXEDCLK is used as FTM input clock. FIRC_DIV_1 is selected as RTC_CLK output which is "FTM_CLOCK_SOURCE_FIXEDCLK".

But the result is the same as previous. When I change the prescaler in FTM registers, clock changes to : 32MHz, 16MHz, 8MHz , .... . It seems when choosing frequency of the FIRC (48MHz) as FTM input in any method (either with PCC_FLEXTMRn[PCS] or Fixed frequency clock) the clock changes from 48MHz to 32MHz !!!

P.S. I monitor the RTC_CLK in CLKOUT pin and there is a 48MHz signal which is correct !

meanwhile reading RM, I see 2 points:

1. as you can see in below image, there is a synchronizer block between External clocks (which can include FIRC_DIV_1, SIR_DIV_1, SPLL_DIV_1 or TCLK[0:1]) and the FTM input. Unfortunately additional explanation about this block is not available and maybe this block is cause of the my question in first post.

Has anybody any idea?

2. In continue, there is one paragraph about this block which is vague also:

what is purpose of these details about FTM?

Thanks.

Hi JeorgeB,

According to the description of "47.5.1.1 Counter clock source" and "Table 27-9. Peripheral module clocking":

The frequency of the fixed frequency clock(RTC_CLK) must not exceed 1/2 of the FTM input clock frequency(FTM System clock SYS_CLK)..

The frequency of the external clock source(TCLK0 \ TCLK1 \ TCLK2 \ SOSCDIV1_CLK \ SIRCDIV1_CLK \ FIRCDIV1_CLK \ SPLLDIV1_CLK) must not exceed 1/4 of the FTM input clock frequency(FTM System clock SYS_CLK).

Due to: SYS_CLK = CORE_CLK = 80MHz

So:

Frequency of external clock source should not exceed 20MHz.

Frequency of fixed clock source should not exceed 40MHz.

But it seems to conflict with your test results. Would you please attached your test project? So that I can test it faster.

Best Regards,

Robin