- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32G

- :

- where is bootloader sample project using S32 Design Studio

where is bootloader sample project using S32 Design Studio

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello

I have a S32G-VNP-RDB2 board.

I have to develop bootloader.

so I have download Platform_Software_Integration_S32G3XX_2022_02.

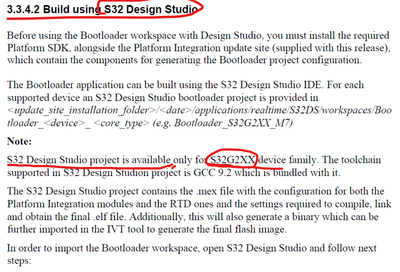

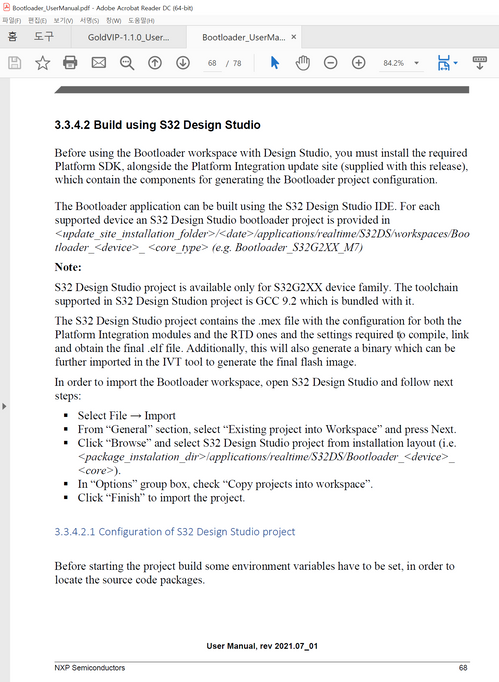

I would like to do item 3.3.4.2 in bootloader_UserManual.pdf below.

But I can not find S32DS folder.

I have Tresos folder in realtime folder below.

I want to know where the s32DS folder is.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

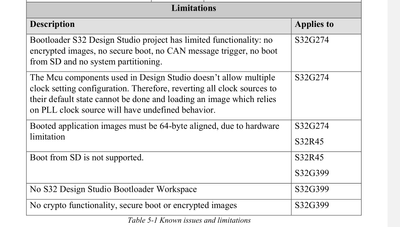

No S32DS support for that release as well due to the following limitation:

The Mcu components used in Design Studio doesn’t allow multiple

clock setting configuration. Therefore, reverting all clock sources to

their default state cannot be done and loading an image which relies

on PLL clock source will have undefined behavior.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please refer to page 83:

There's no support for S32 Design Studio for the release you are trying to use. Also, please make sure to check the hardware prerequisites as well, because the board you are using doesn't support S32G3XX.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My board is S32G2xx in S32G-VNP-RDB2.

Please see the note below.

The S32DS is said to be able to use the S32G2xx.

Additionally, my Bootloader_UserManual.pdf does not have 83 pages.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You state above "Platform_Software_Integration_S32G3XX_2022_02.", which is an S32G3XX release and hence referring to the user manual pertaining to that release. Can you please confirm that?

Even though the DS support is mentioned in that chapter, there may be some limitations (refer to "Known issues and limitation").

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the advice. It was my mistake.

I have another Platform_Software_Integration_S32G2XX_2021_09.

Currently available for download S32G2xx, the latest version will be Platform_Software_Integration_S32G2XX_2021_09.

The same content is also in the Bootloader.pdf file of Platform_Software_Integration_S32G2XX_2021_09.

Can you check again based on this version?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No S32DS support for that release as well due to the following limitation:

The Mcu components used in Design Studio doesn’t allow multiple

clock setting configuration. Therefore, reverting all clock sources to

their default state cannot be done and loading an image which relies

on PLL clock source will have undefined behavior.