- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32G

- :

- Scheck AHB Test - Fault Injection and detection

Scheck AHB Test - Fault Injection and detection

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Scheck AHB Test - Fault Injection and detection

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Currently, Executing shutdown scheck AhbTest_CM7_0 Test(cm7_0_tcm_ahb

_slice_err_inj_0).

I have observed that the respective test is injecting a fault at u32CtrlRegAddr = 0x4007CA28 with mask u32CtrlRegMask = 0x1, but it's failing at sCheck_DetectAndClearFault.

I have observed that the status register, u32StatRegAddr = 0x4007CAFC, with mask u32StatRegMask = 0x00200000, doesn't get updated during the test.

It can refer to the snippet.

Q1. Should the status register update the moment the control register is updated with fault injection?

Q2. any prerequisites that shall be implemented?

Regards,

Irshad

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Irshad2225,

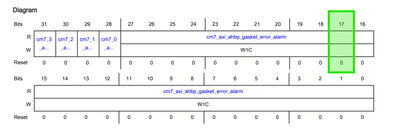

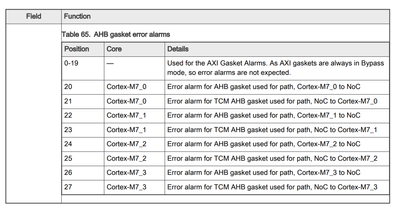

Thanks for reaching out to us. Regarding your problem, Can you share the list of errors you are passing in the first argument of sCheck_AhbTest_CM7? This is, sCheck_ErrorContainerType * pErrorContainer, I ask this, because as per your post, you expect the bit 0x0002_0000 (bit 17), which is a read only bit (with write-1-clear config) in the Cortex-M7 AXI Parity Error and AHBP Gasket Error Alarm (CM7_AXI_AHBP_GASKET_ERROR_ALARM) register:

Can you confirm if your configuration is valid?

One other thing that may help us is testing the same AHB test configuration but instead of performing it during shutdown, run it during boot or normal operation, in the past I have seen some test fail only during shutdown, please test that setup and let me know if you see the same behavior.

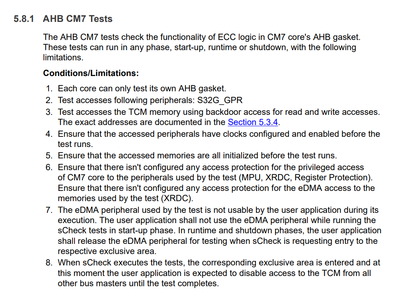

As a side note, this are the prerequisites for the AHB CM7 test:

Please check if they are met in your setup.

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

0x0,

0x0,

0x0,

0x0,

0x0,

0x0,

0x00,

0x0,

0x0,

0x0,

0x0,

0x0,

0x0,

0x0}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Irshad2225

Thanks for the information. However, I still don't fully understand your request, After reviweing the code I don't see why are you expecting the register at 0x4007CAFC (CM7_AXI_AHBP_GASKET_ERROR_ALARM) to set its 17th bit:

that part of the register is write-1-clear, therefore, "writing 1" to the register, it will be cleared.

Which is the behavior your are seeing correct?

Let me know if I am understanding your explanation correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As sCheck_DetectAndClearFault API is checking for the fault handler activation in u32StatRegAddr = 0x4007CAFC, with mask u32StatRegMask = 0x00200000 and it's getting failed.

Wanted to know what might have caused the issue.

One more question, is there any suggested place where scheck_shutdown tests can be performed in the SHUTDOWN sequence?, Currently, I have kept in EcuM_OnGoOffOne().

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Irshad2225,

Sorry for the very late reply. Regarding your last question, I'm assuming you refer to function sCheck_ExecuteShutdownTests, checking the manual for that particular API function, I don't see any special place in which to put the function:

It only needs to be called before shutting down or going to sleep mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have performed AHB test at the startup test, observed the same thing, the control register getting updated and not the status register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content