- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32G

- :

- Re: S32G2 with RTD 3.0.x drivers and QSPI Flash: how to disable AHB buffer ?

S32G2 with RTD 3.0.x drivers and QSPI Flash: how to disable AHB buffer ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

am working on an S32G274A board (bt not one of the NXP products, it is manufactured by a 3rd party), it has a Micron

MT35XU512ABA octal serial NOR flash mounted. for the M7_0, I have to adapt the RTD/MCAL fls configuration LUT sequences, until now with mediocre success.

(current RTD version: SW32G_RTD_4.4_3.0.2_HF01)

Reading and writing the special configuration registers in STRD mode (when booting) seems to work. Then I switch to octal DDR mode, but either my write or my read sequences

fail to work correctly. No errors reported, but I can not confirm by reading back what I have just written to the flash memory.

it is not an issue wth the write enable, the RDT drivers set this automatically.

to rule out that it has something to do with the AHB buffer, I would like to disable the AHB feature (the S32G2 reference manual sugessts that there is the option between

- IP command read (I would like to try that)

- AHB read (used in all examples from NXP)

I was wondering how to disable or remove the AHB feature from my configuration (in Tresos). But removing the subcontaines in the AHB configuration yields a tool error.

--> How do I get to use a bare IP command read ?

And follow up question: are there examples with Micron flash configurations available (for the M7) ?

thanks and best regards,

Stefan

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

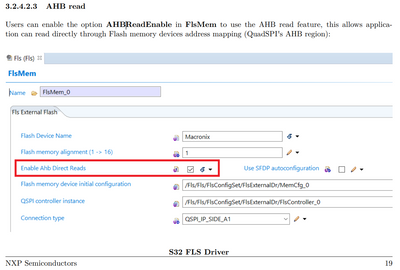

The User Manual for the FLS driver provides information on regards of the AHB usage under a read command. The following snip is provided from the User Manual:

AHB can only be used under a read command, for which any write commands should not be valid through AHB. Also, the following limitation is shown under the User Manual:

"Users must add and use MPU to configure the QSPI AHB address space as device memory to prevent speculative reads in this region"

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just use IP commands, AHB doesn't have to be disabled.

DDR at high speeds needs special care. Data learning pattern or other means to fine tune sample point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kef2 ,

understood, but if your suggestions is to use IP commands directly (in a programmatic way): I don't have that freedom. I am working on a classic AUTOSAR system with the NXP RTD driver stack acting as the AUTOSAR MCAL layer. My entry point to the flash driver is Fls_Write(), Fls_Read(), Fls_Erase() etc. Whatever is hapenning inside the driver can only be controlled through the configuration of the NXP RTD stack through the Tresos tool.

So I was wondering what to configure in Tresos / the RDT offline configuration to make it use only IP commands and ignore the AHB buffer.

best regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can't help you with Autosar, but I believe that in your situation suspect #1 is DDR mode, not AHB. Did you try reducing QSPI clock to 20MHz or even less?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kef2 ,

in the meantime I can confirm that register read, data read and page program are working in octal DDR mode, so I guess my DDR settings should be more or less correct.

And I can see these results in the AHB buffer, hence I decided to trust the AHB for the moment.

However, I don't get a sector erase to work, I have opened a different thread for this, since it is a different topic.

it @every body else out there: it would still be interesting to know how the selection between AHB and IP access is controlled in the NXP RDT drivers withg the help of Tresos. Any hints welcome.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The User Manual for the FLS driver provides information on regards of the AHB usage under a read command. The following snip is provided from the User Manual:

AHB can only be used under a read command, for which any write commands should not be valid through AHB. Also, the following limitation is shown under the User Manual:

"Users must add and use MPU to configure the QSPI AHB address space as device memory to prevent speculative reads in this region"

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

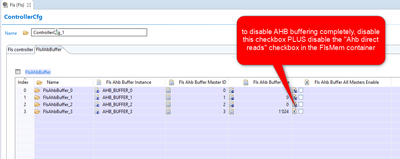

Hi @Daniel-Aguirre ,

Thank you for the hint, the checkbox in the FlsMem container I had missed (I was focused on the Fls ConrollerCfg->FlsAhbBuffer container).

To switch the AHB buffering off completely, I noticed that also the "Fls Ahb Buffer ALl Masters enable" checkbox must be disabled in the ControllerCfg contrainer (plus the one that you mentioned), then it works.

Thx again,

best regards,

Stefan