- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32G

- :

- Re: S32G2 OCOPT programming

S32G2 OCOPT programming

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

We don't have any configuration switch in our hardware to burn the eFUSE configurations. For this reason we want to burn it via software and found OCOTP peripheral module and we are checking if it is right for our hardware since it is a one time operation and cannot be taken back.

Our confusion comes from the register addresses defined in the software;

#define OCOTP_GP6_127_96 0x384U

#define OCOTP_GP6_159_128 0x388U

#define OCOTP_GP6_127_96_SHADOW_REGISTER 97U

#define OCOTP_GP6_159_128_SHADOW_REGISTER 98U

#define CRC0_EFUSE_ADD 0x2DCU

#define CRC0_SHADOW_REGISTER 55U

What does OCOTP_GP6_127_96 mean in the register? We want to program the field BOOT_CFG1[31:0] - ADDR=0x234 field. Which shadow register value corresponds to this?

Thank you

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Below will be some comments on regards of your questions:

Q1 > What does OCOTP_GP6_127_96 mean in the register?

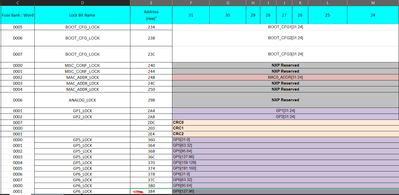

[NXP]: This is related to the mapping of that specific FUSE address. We can see that under the S32G2_Fuse_Map_Table.xlsx file embedded under the S32G2 RM the following address is provided for GP6[127:96]:

For which 0x384 is the address of GP6[127:96].

Q2 > We want to program the field BOOT_CFG1[31:0] - ADDR=0x234 field. Which shadow register value corresponds to this?

[NXP]: Seeing the file mentioned before, the address should be the one you are mentioning (0x234). For the shadow register, we understand that the calculation is as follows:

Shadow Register = (Address - 0x200) / 4;

We can verify this by using the registers you are showing:

- GP6_127_96 Shadow Register = (0x384 - 0x200) / 4 = 0x184 / 4 = 0x61 = 97

- GP6_159_128 Shadow Register = (0x388 - 0x200) / 4 = 0x188 / 4 = 0x62 = 98

Don't know if this helps.

Also, as you are mentioning this is a one-time operation and cannot be taken back, for which care should be taken with the configuration being chosen. We can recommend contacting your local NXP FAE/DFAE/representative for confirmation on these settings.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Below will be some comments on regards of your questions:

Q1 > What does OCOTP_GP6_127_96 mean in the register?

[NXP]: This is related to the mapping of that specific FUSE address. We can see that under the S32G2_Fuse_Map_Table.xlsx file embedded under the S32G2 RM the following address is provided for GP6[127:96]:

For which 0x384 is the address of GP6[127:96].

Q2 > We want to program the field BOOT_CFG1[31:0] - ADDR=0x234 field. Which shadow register value corresponds to this?

[NXP]: Seeing the file mentioned before, the address should be the one you are mentioning (0x234). For the shadow register, we understand that the calculation is as follows:

Shadow Register = (Address - 0x200) / 4;

We can verify this by using the registers you are showing:

- GP6_127_96 Shadow Register = (0x384 - 0x200) / 4 = 0x184 / 4 = 0x61 = 97

- GP6_159_128 Shadow Register = (0x388 - 0x200) / 4 = 0x188 / 4 = 0x62 = 98

Don't know if this helps.

Also, as you are mentioning this is a one-time operation and cannot be taken back, for which care should be taken with the configuration being chosen. We can recommend contacting your local NXP FAE/DFAE/representative for confirmation on these settings.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Daniel-Aguirre ,

thank you for your quick response. It made me understand the underlying logic.

How do we map from 0x234 to 0x384? That is, the way going from BOOT_CFG1 to GP6[127:96] ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback. We don't seem to understand this last request. Can you help us elaborate more on the following comment:

"How do we map from 0x234 to 0x384? That is, the way going from BOOT_CFG1 to GP6[127:96] ?"

Why are you trying to map BOOT_CF1 to GP6?

Please, let us know.