- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Re: Which result is better for S12ZVCA CAN Setup ?

Which result is better for S12ZVCA CAN Setup ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

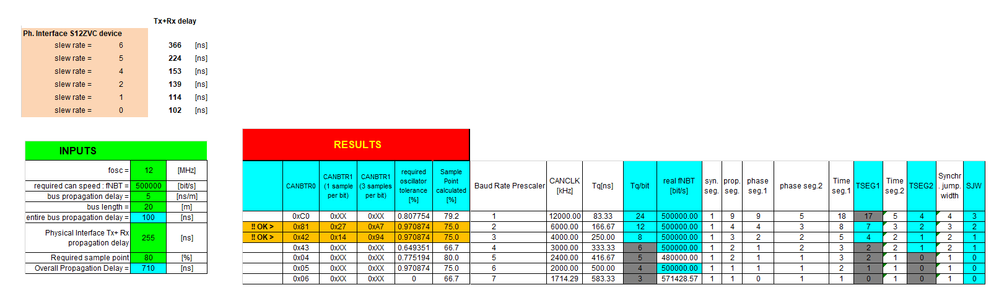

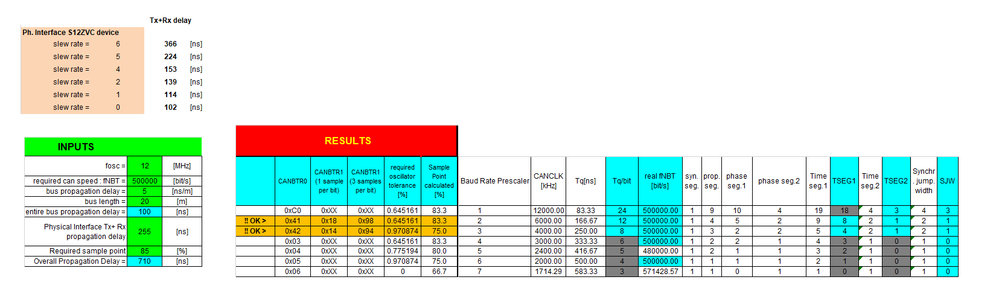

My project requirement as follow:

Application: Automotive

MCU: S12ZVCA19MLF

External Crystal: 12MHz

CAN Bit Rate: 500Kbps

CAN Cable Length: < 20m

Slew Rate: 4 (Which value is the best on this project?)

Is the input correct or not?

Which result is best? What do you recommend?

Best Regard,

Aaron

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Almost,...

Slew rate 4 requires Rx+Tx propagation delay 153ns. (You left there 255 ns) However, it does not change anything in result in this case.

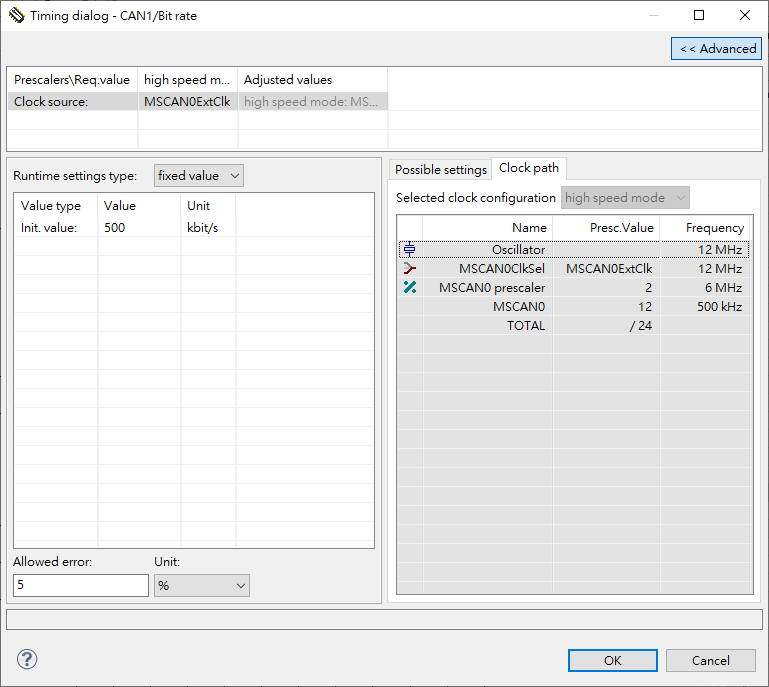

I suppose you want to use oscillator clock as a CAN clock. (CANCTL1_CLKsrc=0)

One think which has interested me is the change of required sample point and the change in result. The file does not use dynamic calculations to get absolutely optimum solution and this approach has provided closer setup to 80% sample point than directly entered input for 80%. The change of sample point makes different spilitting of segments. (probably in some future I will rebuilt the file for dynamical calculations)

What I would like also to mention is the requirement on sample point. I mean whether you accept later sample point or not. 83.3% is closer to 80% than 75 %. (but...youl see bellow)

I have stolen from another article: "An early sample point decreases the sensitivity to oscillator tolerances and allows lower-quality oscillators. A late sample point allows for a longer signal propagation time and therefore a longer bus. A later sample point is useful for non-ideal bus topologies. The CAN-in-Automation user’s group makes recommendations of where the sample point should be for various bit rates, with 87.5% the most common."

If you require sample point 80% (based on, I think, required input) then I would use use result line for 83.3% (CANBTR0=0x41, CANBTR1=0x18)

Best regards,

Ladislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Almost,...

Slew rate 4 requires Rx+Tx propagation delay 153ns. (You left there 255 ns) However, it does not change anything in result in this case.

I suppose you want to use oscillator clock as a CAN clock. (CANCTL1_CLKsrc=0)

One think which has interested me is the change of required sample point and the change in result. The file does not use dynamic calculations to get absolutely optimum solution and this approach has provided closer setup to 80% sample point than directly entered input for 80%. The change of sample point makes different spilitting of segments. (probably in some future I will rebuilt the file for dynamical calculations)

What I would like also to mention is the requirement on sample point. I mean whether you accept later sample point or not. 83.3% is closer to 80% than 75 %. (but...youl see bellow)

I have stolen from another article: "An early sample point decreases the sensitivity to oscillator tolerances and allows lower-quality oscillators. A late sample point allows for a longer signal propagation time and therefore a longer bus. A later sample point is useful for non-ideal bus topologies. The CAN-in-Automation user’s group makes recommendations of where the sample point should be for various bit rates, with 87.5% the most common."

If you require sample point 80% (based on, I think, required input) then I would use use result line for 83.3% (CANBTR0=0x41, CANBTR1=0x18)

Best regards,

Ladislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ladislav,

Very useful. Thank you very much.

Yes, I used MSCAN0ExtClk.

Do you recommend using a higher frequency of the external crystal? Ex: 16MHz or 20MHz?

Best Regard,

Aaron