- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 产品论坛

- :

- S12 / MagniV微控制器

- :

- Re: S12ZVLA64 EMC CE TEST ISSUE

S12ZVLA64 EMC CE TEST ISSUE

S12ZVLA64 EMC CE TEST ISSUE

Dear NXP Enginner:

In our project, the NXP MCU S912ZVLA64F0MLF is used;

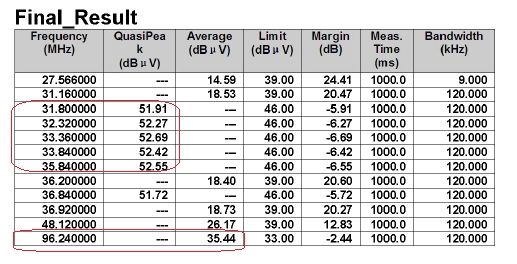

At present stage, the EMC CE test failed,as below, the failure frequencies are between the range of 31.8~35.8Mhz, and 96.2Mhz point;

We checked our design(circuit&programm) carefully, while no source of upper frequency points were found.There are just MCU,SENSOR and CAN phy ,sensor and can phy just work in 500~900Khz frequence.schematic as below:

One doubt way is:

The DC regulator is internally intergated in the MCU (S912ZVLA64F0MLF) ;

Wheather the upper relate frequency are generated from the internal Regulator Block?

Besides,any other possible source of the relate frequency?

It is urgent ,Could you help me ?thanks!

Hello,

I don't think this is caused by the regulator if you use the recommended decoupling capacitors.

Speaking of the regulator, if you use the external ballast transistor, the internal one must be disabled.

CPMUVREGCTL_INTXON = 0.

Have you tried changing the PLL/BUS clock frequency?

What is the frequency of the crystal?

Do you use the oscillator in Loop Controlled Mode or in Full-swing Mode?

The Full-swing mode offer higher immunity against noise injection on the cost of increased emission.

Please refer to AN5084 Hardware Design Guidelines for the S12ZVL Microcontrollers

3 Power management

5.2 Suggestions for the PCB layout of oscillator circuit

13 General Board Layout Guidelines

13.3 EMI/EMC and ESD Considerations for Layout

Regards,

Daniel