- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- S12XEP100 RTI ISR Problems

S12XEP100 RTI ISR Problems

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S12XEP100 RTI ISR Problems

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello community,

i am trying to get the RTI to work on my S12XEP100. I am getting the clock from a 8 MHz crystal and i want to run the INT every 1ms. I am Using CodeWarrior IDE 5.9.0.

I read Datasheet and configured the RTI as followed:

void RTI_init(void)

{

RTICTL_RTDEC = 1; // Decimal or Binary Divider Select Bit (decimal based divider value)

//Divider = 8000 (RTI Time = 1ms)

RTICTL_RTR0 = 1; // Real Time Interrupt Modulus Counter Select Bit 0

RTICTL_RTR1 = 1; // Real Time Interrupt Modulus Counter Select Bit 1

RTICTL_RTR2 = 0; // Real Time Interrupt Modulus Counter Select Bit 2

RTICTL_RTR3 = 0; // Real Time Interrupt Modulus Counter Select Bit 3

RTICTL_RTR4 = 1; // Real Time Interrupt Prescale Rate Select Bit 4

RTICTL_RTR5 = 0; // Real Time Interrupt Prescale Rate Select Bit 5

RTICTL_RTR6 = 0; // Real Time Interrupt Prescale Rate Select Bit 6

CRGINT_RTIE = 1; // Real Time Interrupt Enable Bit

EnableInterrupts;

}

so far so good... now i am trying to create an ISR for the RTI but this where problems begin....

I have searched in S12x examples pack on NXP page how to create an ISR and found an example for creating an ISR for ADT0. Here is what i found:

//==============================================================================

// ATD0_ISR

//==============================================================================

#pragma CODE_SEG NON_BANKED

interrupt 22 void ATD0_ISR(void)

{

//code

}

#pragma CODE_SEG DEFAULT

Now the question:

Where can i find the information how i have to change the ATD0_ISR code to get an RTI ISR?

Where can i find the information whitch Nuber i need? (for ADT0 this is 22 but what for RTI?)

Where can i find the information for the ISR Name i need? (for ADT0 this is ATD0_ISR but what for RTI?)

Thanx!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please look into https://community.nxp.com/docs/DOC-329209

There is many examples to easy understand how it works:

Also I have attached a few I use in explanation....

For example:

#pragma CODE_SEG NON_BANKED

interrupt 7 void RTI_ISR(void)

{

ARMCOP=0x55; // kick the dog

ARMCOP=0xAA;

CRGFLG = 0x80; // Clear the flag

PORTB=~PORTB;

}

#pragma CODE_SEG DEFAULT

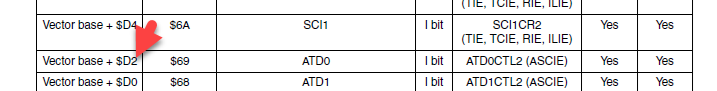

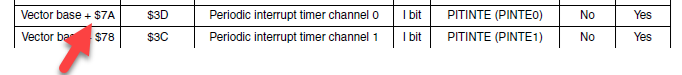

If you go into Table 1-14. Interrupt Vector Locations then you can also use following approach which explains how to get interrupt number.

//====================================

#pragma CODE_SEG NON_BANKED

interrupt ((0xFE-0xD2)/2) void ATD0_ISR(void) // 0xD2 is an offset presented in the table for given interrupt

{

}

#pragma CODE_SEG DEFAULT

//====================================

#pragma CODE_SEG NON_BANKED

interrupt ((0xFE-0xF0)/2) void RTI_ISR(void) // interrupt ((0xFE-0xF0)/2) the same as interrupt 7

{

}

#pragma CODE_SEG DEFAULT

//====================================

#pragma CODE_SEG NON_BANKED

interrupt ((0xFE-0xA2)/2) void can2Rx_ISR(void)

{

}

#pragma CODE_SEG DEFAULT

//====================================

I would like also to direct you to an example XEP100-INT-INTERRUPTNUMBER-CW51

#define SET_CPU_PRIORITY(vec_adr, priority) \

INT_CFADDR= (vec_adr) & 0xF0; \

INT_CFDATA_ARR[((vec_adr) & 0x0F) >> 1]= (priority)

#define PIT0 0x7A // vector address

Code:

…

…

SET_CPU_PRIORITY(PIT0, 1); // set to HW priority and the lowest level

…

…

SET_CPU_PRIORITY(PIT0, 4); // change HW priority level

…

…

Note, another example usinf TRAPPROC as definition of the interrupt together with interrupt function vector defined in the prm file (at the bottom of the file) can be seen in XEP100-INT-TRAPPROC-CW51

Which presents how to set interrupt priority level from 0 to 7. Let’s mention that level 0 disables interrupt even it is enabled in the control register of given peripheral.

The easiest way is to use vector table from the reference manual and use following principle:

If this does not answer your question(s), or I have forgotten something, or if you need more assistance, please contact me again.

- This issue will auto close in 7 days upon no reply.

Best Regards, Ladislav