- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Re: MC9S12G240MLF "margin levels"

MC9S12G240MLF "margin levels"

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MC9S12G240MLF "margin levels"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If we consider "1" to be the erased state for a bit and "0" to be the programmed state, then we can say that high levels are erased and low levels are programmed.

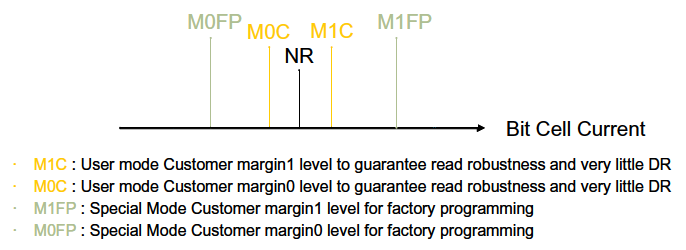

I think I get the basis of margin levels, in so far as setting the margin level to "1" increases the threshold to make it more likely to read a "0". We would use it after an erase to make sure there was a margin between the normal read level and the programmed voltage level to guarantee that we would read a "1" everywhere.

And of course the opposite is true of "0". We would use a margin level of "0" that would reduce the threshold, to make sure that bits that have been programmed still come back as "0" even after the threshold had been lowered.

My question is when do "user" margin levels apply and when do "field" margin levels apply? According to data sheets they both apply on subsequent reads?

Also, "field" margin levels can be set more sever than "user" margin levels. What is the difference in programming and erase methods that make "field" margin levels applicable over "user" levels?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Paul,

Your understanding of margin read is correct.

The difference between "user" margin level and "field" margin level is just setting of internal threshold for reading.

The "field" margin level could be set only by Set Field Margin Level command for unsecured MCU in special mode. Field margin levels must only be used during verify of the initial factory programming.

However "user" margin level could be set by Set Field Margin Level and Set User Margin Level commands. Set User Margin Level command could be executed by MCU in normal mode (despite on security) and by unsecured MCU in special mode.

So, if you detect problem with "field" margin level in factory, P-Flash/EEPROM is probably wrongly programmed (In this case NVM should be reprogrammed) and if you detect problem with "user" margin level in the field, P-Flash/EEPROM is probably close to Data retention limit (In this case MCU may signalize that NVM should be reprogrammed or MCU/module replaced). In extreme case I could imagine case with two identical copies of code/data in NVM and MCU may in that case reprogram itself.

How to use "user" margin level:

We could use for example CRC checksum stored it somewhere in P-Flash or EEPROM.

We could set User Margin-1 Level, calculate CRC checksum over whole flash and compare it with stored value. After that we could set User Margin-0 Level, calculate CRC checksum over whole flash and compare it with stored value. After that we should not forget set margin level back to Normal Level. If both comparing fits, NVM looks ok. If any of comparing fails, MCU should signalize error,…

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

?Never mind. I reread your response. So the difference between the two is when the command can be called. Am I right. Thanks. Paul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

?Hi Radek

I understand that to set field margin level you use the field margin level command etc. My question is when do they apply?

For example I set the field margin level, then I set the user margin level, then I do a read. Which margin level applies?

Paul.