- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Re: t1042 DDR3 memory lose data

t1042 DDR3 memory lose data

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

t1042 DDR3 memory lose data

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

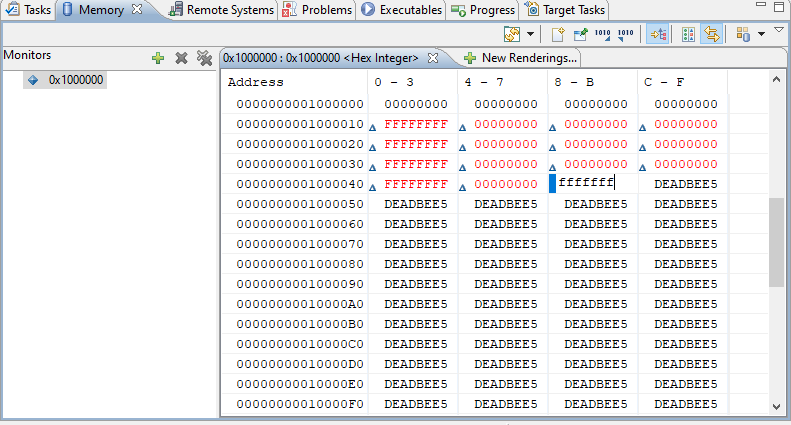

I have t1042 custom board. i use QCVS to check initialization data, and calibarate memory. it passed all memory write-read tests. But when i start dubugger memory does not work. I see my custom DEADBEE5 initial data in memory monitor, but when i write FFFFFFFF most of cell becomes 00000000. and i cant run any application from RAM. i have several of MT18KSF51272HZ-1G6K2ZF SO-DIMM module the same behavior.

###############################################################################

## Target initialization file - DDR controller 1 section #

##

## Copyright : 2016 NXP, Inc. All Rights Reserved.

## SOURCE DISTRIBUTION PERMISSIBLE as directed in End User License Agreement.

##

## http : www.nxp.com

## mail : support@nxp.com

################################################################################

proc value_of {x} {

return $x

}

# DDR Controller 1 Registers

# DDR_SDRAM_CFG

mem i:0xFE008110 = [value_of 0x67200000]

# CS0_BNDS

mem i:0xFE008000 = [value_of 0x7F]

# CS1_BNDS

mem i:0xFE008008 = [value_of 0x0100017F]

# CS2_BNDS

mem i:0xFE008010 = [value_of 0x018001BF]

# CS3_BNDS

mem i:0xFE008018 = [value_of 0x01C001FF]

# CS0_CONFIG

mem i:0xFE008080 = [value_of 0x80004302]

# CS1_CONFIG

mem i:0xFE008084 = [value_of 0x80044302]

# CS2_CONFIG

mem i:0xFE008088 = [value_of 0x00010202]

# CS3_CONFIG

mem i:0xFE00808C = [value_of 0x00010202]

# CS0_CONFIG_2

mem i:0xFE0080C0 = [value_of 0x00]

# CS1_CONFIG_2

mem i:0xFE0080C4 = [value_of 0x00]

# CS2_CONFIG_2

mem i:0xFE0080C8 = [value_of 0x00]

# CS3_CONFIG_2

mem i:0xFE0080CC = [value_of 0x00]

# TIMING_CFG_3

mem i:0xFE008100 = [value_of 0x01071000]

# TIMING_CFG_0

mem i:0xFE008104 = [value_of 0x8055000C]

# TIMING_CFG_1

mem i:0xFE008108 = [value_of 0xBCB48C57]

# TIMING_CFG_2

mem i:0xFE00810C = [value_of 0x00411118]

# DDR_SDRAM_CFG_2

mem i:0xFE008114 = [value_of 0x00401050]

# DDR_SDRAM_MODE

mem i:0xFE008118 = [value_of 0x00441A71]

# DDR_SDRAM_MODE_2

mem i:0xFE00811C = [value_of 0x00180000]

# DDR_SDRAM_MODE_2

mem i:0xFE00811C = [value_of 0x00180000]

# DDR_SDRAM_MODE_2

mem i:0xFE00811C = [value_of 0x00180000]

# DDR_SDRAM_MODE_3

mem i:0xFE008200 = [value_of 0x00]

# DDR_SDRAM_MODE_4

mem i:0xFE008204 = [value_of 0x00]

# DDR_SDRAM_MODE_5

mem i:0xFE008208 = [value_of 0x00]

# DDR_SDRAM_MODE_6

mem i:0xFE00820C = [value_of 0x00]

# DDR_SDRAM_MODE_7

mem i:0xFE008210 = [value_of 0x00]

# DDR_SDRAM_MODE_8

mem i:0xFE008214 = [value_of 0x00]

# DDR_SDRAM_MD_CNTL

mem i:0xFE008120 = [value_of 0x00000000]

# DDR_SDRAM_INTERVAL

mem i:0xFE008124 = [value_of 0x18600618]

# DDR_DATA_INIT

mem i:0xFE008128 = [value_of 0xDEADBEE5]

# DDR_SDRAM_CLK_CNTL

mem i:0xFE008130 = [value_of 0x02000000]

# DDR_INIT_ADDR

mem i:0xFE008148 = [value_of 0x00000000]

# DDR_INIT_EXT_ADDR

mem i:0xFE00814C = [value_of 0x00000000]

# TIMING_CFG_4

mem i:0xFE008160 = [value_of 0x00220001]

# TIMING_CFG_5

mem i:0xFE008164 = [value_of 0x04401400]

# DDR_ZQ_CNTL

mem i:0xFE008170 = [value_of 0x89080600]

# DDR_WRLVL_CNTL

mem i:0xFE008174 = [value_of 0x8655F605]

# DDR_SR_CNTR

mem i:0xFE00817C = [value_of 0x00000000]

# DDR_WRLVL_CNTL_2

mem i:0xFE008190 = [value_of 0x0609050F]

# DDR_WRLVL_CNTL_3

mem i:0xFE008194 = [value_of 0x0B0D0B0A]

# DDR_ERR_DISABLE

mem i:0xFE008E44 = [value_of 0x00]

# DDR_ERR_INT_EN

mem i:0xFE008E48 = [value_of 0x1D]

# DDR_ERR_SBE

mem i:0xFE008E58 = [value_of 0x00010000]

# DDRCDR_1

mem i:0xFE008B28 = [value_of 0x80040000]

# DDRCDR_2

mem i:0xFE008B2C = [value_of 0x01]

# DDR_SDRAM_CFG_3

mem i:0xFE008260 = [value_of 0x00]

# TIMING_CFG_6

mem i:0xFE008168 = [value_of 0x00]

# TIMING_CFG_7

mem i:0xFE00816C = [value_of 0x00]

# TIMING_CFG_8

mem i:0xFE008250 = [value_of 0x00]

# DESKEW_CNTL

mem i:0xFE0082A0 = [value_of 0x00]

# DQ_MAP0

mem i:0xFE008400 = [value_of 0x00]

# DQ_MAP1

mem i:0xFE008404 = [value_of 0x00]

# DQ_MAP2

mem i:0xFE008408= [value_of 0x00]

# DQ_MAP3

mem i:0xFE008400 = [value_of 0x00]

# DDR_SDRAM_MODE_9

mem i:0xFE008220 = [value_of 0x00]

# DDR_SDRAM_MODE_10

mem i:0xFE008224 = [value_of 0x00]

# DDR_SDRAM_MODE_11

mem i:0xFE008228 = [value_of 0x00]

# DDR_SDRAM_MODE_12

mem i:0xFE00822C = [value_of 0x00]

# DDR_SDRAM_MODE_13

mem i:0xFE008230 = [value_of 0x00]

# DDR_SDRAM_MODE_14

mem i:0xFE008234 = [value_of 0x00]

# DDR_SDRAM_MODE_15

mem i:0xFE008238 = [value_of 0x00]

# DDR_SDRAM_MODE_16

mem i:0xFE00823C = [value_of 0x00]

# DDR_SDRAM_RCW_3

mem i:0xFE0081A0 = [value_of 0x00]

# DDR_SDRAM_RCW_4

mem i:0xFE0081A4 = [value_of 0x00]

# DDR_SDRAM_RCW_5

mem i:0xFE0081A8 = [value_of 0x00]

# DDR_SDRAM_RCW_6

mem i:0xFE0081AC = [value_of 0x00]

#Delay before enable

wait 500

#DDR_SDRAM_CFG

mem i:0xFE008110 = [value_of 0xE7200000]

# wait for DRAM data initialization

wait 1000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There was wrong Clock Frequence setting in RCW . Solved.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Following DDR3 setup is used on our development board with the same DIMMlike you use, please try it:

# DDR Controller Setup

# DDR_SDRAM_CFG

mem [CCSR_ADDR 0x8110] = 0x67044000

# DDR_CS0_BNDS

mem [CCSR_ADDR 0x8000] = 0x000000ff

# DDR_CS1_BNDS

mem [CCSR_ADDR 0x8008] = 0x000000ff

# DDR_CS0_CONFIG

mem [CCSR_ADDR 0x8080] = 0x80044302

# DDR_CS1_CONFIG

mem [CCSR_ADDR 0x8084] = 0x80004302

# DDR_CS0_CONFIG_2

mem [CCSR_ADDR 0x80c0] = 0x00000000

# DDR_CS1_CONFIG_2

mem [CCSR_ADDR 0x80c4] = 0x00000000

# DDR_TIMING_CFG_3

mem [CCSR_ADDR 0x8100] = 0x01071000

# DDR_TIMING_CFG_0

mem [CCSR_ADDR 0x8104] = 0x5011000C

# DDR_TIMING_CFG_1

mem [CCSR_ADDR 0x8108] = 0xbcb58c56

# DDR_TIMING_CFG_2

mem [CCSR_ADDR 0x810C] = 0x0040c158

# DDR_SDRAM_CFG_2

mem [CCSR_ADDR 0x8114] = 0x00401111

# DDR_SDRAM_MODE

mem [CCSR_ADDR 0x8118] = 0x00441c70

# DDR_SDRAM_MODE_2

mem [CCSR_ADDR 0x811C] = 0x00980000

# DDR_SDRAM_MODE_3

mem [CCSR_ADDR 0x8200] = 0x00001c70

# DDR_SDRAM_MODE_4

mem [CCSR_ADDR 0x8204] = 0x00980000

# DDR_SDRAM_MODE_5

mem [CCSR_ADDR 0x8208] = 0x00001c70

# DDR_SDRAM_MODE_6

mem [CCSR_ADDR 0x820C] = 0x00000000

# DDR_SDRAM_MODE_7

mem [CCSR_ADDR 0x8210] = 0x00001c70

# DDR_SDRAM_MODE_8

mem [CCSR_ADDR 0x8214] = 0x00000000

# DDR_SDRAM_MD_CNTL

mem [CCSR_ADDR 0x8120] = 0x00000000

# DDR_SDRAM_INTERVAL

mem [CCSR_ADDR 0x8124] = 0x0c300100

# DDR_DATA_INIT

mem [CCSR_ADDR 0x8128] = 0xdeadbeef

# DDR_SDRAM_CLK_CNTL

mem [CCSR_ADDR 0x8130] = 0x02000000

# DDR_INIT_ADDR

mem [CCSR_ADDR 0x8148] = 0x00000000

# DDR_INIT_EXT_ADDRESS

mem [CCSR_ADDR 0x814C] = 0x00000000

# DDR_TIMING_CFG_4

mem [CCSR_ADDR 0x8160] = 0x00000001

# DDR_TIMING_CFG_5

mem [CCSR_ADDR 0x8164] = 0x04401400

# DDR_ZQ_CNTL

mem [CCSR_ADDR 0x8170] = 0x89080600

# DDR_WRLVL_CNTL

mem [CCSR_ADDR 0x8174] = 0xc675f607

# DDR_SR_CNTR

mem [CCSR_ADDR 0x817c] = 0x00000000

# DDR_WRLVL_CNTL_2

mem [CCSR_ADDR 0x8190] = 0x0808090b

# DDR_WRLVL_CNTL_3

mem [CCSR_ADDR 0x8194] = 0x0c0d0e0a

# DDR_DDRCDR_1

mem [CCSR_ADDR 0x8b28] = 0x80000000

# DDR_DDRCDR_2

mem [CCSR_ADDR 0x8b2c] = 0x00000000

# DDR_ERR_DISABLE - DISABLE

mem [CCSR_ADDR 0x8e44] = 0x00000000

# DDR_ERR_SBE

mem [CCSR_ADDR 0x8e58] = 0x00000000

# delay before enable

wait 500

# DDR_SDRAM_CFG

mem [CCSR_ADDR 0x8110] = 0xe7044000

# wait for DRAM data initialization

wait 1500

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

cmdwin::mem i:0xfe0e2084 = 0x0000000F

ccs_write_memory

coreh = [serverh:0;cc_index:0;chain_pos:1]

addr = [space:0x9a;size:4;address_hi:0x00000000;address_lo:0xfe0e2084]

data: (size = 4)

0000000F

ccs_write_memory; ccs_error = 0; duration=1 ms

ccs_read_memory

coreh = [serverh:0;cc_index:0;chain_pos:1]

addr = [space:0x90;size:4;address_hi:0x00000001;address_lo:0x00000000]

data: (size = 256)

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

ccs_read_memory; ccs_error = 0; duration=2 ms

ccs_read_memory

coreh = [serverh:0;cc_index:0;chain_pos:1]

addr = [space:0x92;size:4;address_hi:0x00000000;address_lo:0x0ffffe00]

retry = 1

data: (size = 256)

00000000 00000000 575D0000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

00000000 00000000 00000000 00000000

ccs_read_memory; ccs_error = 47; duration=21 ms

Error message: Scan timeout

ccs_core_run_mode

coreh = [serverh:0;cc_index:0;chain_pos:1]

mode = 11

ccs_core_run_mode; ccs_error = 47

Error message: Scan timeout

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

RCW can be found below.

--------------------------------------

U-Boot 2014.07QorIQ-SDK-V1.7+g659b6a2 (Dec 13 2014 - 18:00:52)

CPU0: T1040E, Version: 1.1, (0x85280011)

Core: e5500, Version: 2.1, (0x80241021)

Clock Configuration:

CPU0:1400 MHz, CPU1:1400 MHz, CPU2:1400 MHz, CPU3:1400 MHz,

CCB:600 MHz,

DDR:800 MHz (1600 MT/s data rate) (Asynchronous), IFC:150 MHz

QE:300 MHz

FMAN1: 600 MHz

QMAN: 300 MHz

PME: 300 MHz

L1: D-cache 32 KiB enabled

I-cache 32 KiB enabled

Reset Configuration Word (RCW):

00000000: 0c18000e 0e000000 00000000 00000000

00000010: 66000002 80000002 ec027000 01000000

00000020: 00000000 00000000 00000000 00032810

00000030: 00000000 0342500f 00000000 00000000

Board: T1040RDB

Board rev: 0x01 CPLD ver: 0x09, vBank: 0

I2C: ready

SPI: ready

DRAM: Initializing....using SPD

Detected UDIMM 18KSF51272AZ-1G6K1

4 GiB (DDR3, 64-bit, CL=11, ECC on)

DDR Chip-Select Interleaving Mode: CS0+CS1

...

--------------------------------------

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It does not work.

ccs_write_register

coreh = [serverh:0;cc_index:0;chain_pos:0]

index = 210014

count = 1

size = 4

value: (size = 4)

0342500F

ccs_write_register; ccs_error = 0; duration=2 ms

ccs_write_register

coreh = [serverh:0;cc_index:0;chain_pos:0]

index = 210015

count = 1

size = 4

value: (size = 4)

00000000

ccs_write_register; ccs_error = 0; duration=2 ms

ccs_write_register

coreh = [serverh:0;cc_index:0;chain_pos:0]

index = 210016

count = 1

size = 4

value: (size = 4)

00000000

ccs_write_register; ccs_error = 0; duration=1 ms

ccs_reset_to_debug

serverh = 0

cc = 0

ccs_reset_to_debug; ccs_error = 39

Error message: T1040: Scan timeout

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

memory does not work.

cs_core_run_mode

coreh = [serverh:0;cc_index:0;chain_pos:1]

mode = 11

ccs_core_run_mode; ccs_error = 47

Error message: Scan timeout

Can you provide your RCW?