- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Re: PLL disabled in T2081 custom board

PLL disabled in T2081 custom board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PLL disabled in T2081 custom board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a custom board with sys_clk = 66.66 MHz, ddr_clk=66.6MHz.

And Hard coded RCW is used for board bring up as we dont have programmed flash yet.

Through scope we have seen that the T2081 has come out of Reset power on sequence.

1. But i still get in PLL status registers "PLL disabled"

2. No output at "clk_out" even when configured proper clock domain control status register is programmed?

3. I am able to alter the register contents, toggled GPIO, able to program CPC RAM, Transmitted data on UART then why it shows PLL disabled?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Which exactly RCW is used?

2) Have you provided SerDes reference clocks? What are their frequencies?

3) What are values of the registers showing the "PLL disabled"?

4) What you have done to output the CLK_OUT?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. POR Hard coded RCW used "0x1001 1101" used with sys_clk= ddr_clk=66.67 MHz option as per reference manual

2. SERDES reference clock we are not using, disabled it.

3.Clocking_PLLCnGSR register shows PLL disabled

4. Programmed 15th bit of "Clocking_CLKPCSR"to have output at clk_out

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please program a valid RCW corresponding to your configuration into a flash and test.

The issue can be connected with the hard-coded RCW settings where several SerDes PLLs are enabled - i.e. valid SerDes reference clocks must be applied.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Fedor,

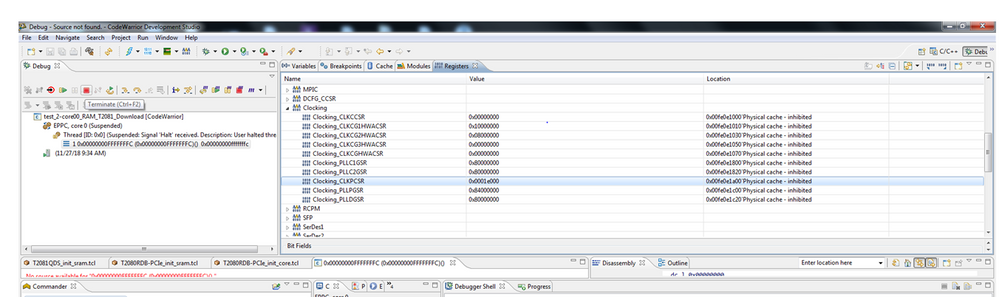

Plese look into the snap of the clock status register.

Clocking_PLLCnGSR =0x80000000. Showing PLL disabled.

1. Does Clocking_PLLCnGSR show status of SERDES PLLs? (Clocking_PLLCnGSR shows the PLL status of PLL1 and PLL2 of CGA only i thought as per clocking diagram in page 222 of T2080 reference manual )

2. Where are SERDES PLLs located? Is it inside SERDES module inside T2080?

3. I am giving Hard Coded RCW. Can i disable the SERDES PLL through JTAG configuration file (to overwrite hard coded RCW )

4. If SERDES PLLs are powered down, wil it still check for proper SERDES REFerence input clocks?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please program a valid RCW corresponding to your configuration into a flash and test.