- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hello,

I am trying to bring up a custom board with the LS1046A.

The boot source is set to the SD Card.

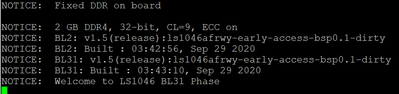

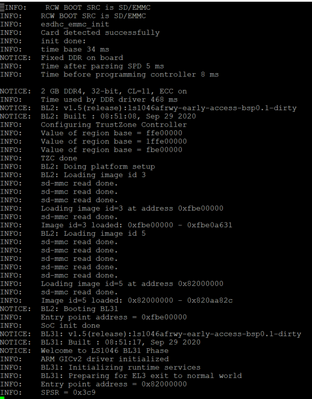

The boot process is starting until "Welcome to LS1046 BL31 Phase" then the board hangs.

What could be the possible root cause for this behaviour?

已解决! 转到解答。

Hello,

So, I finally found where was the error without help of NXP.

To boot on LS1046 with different DDR4:

- RCW => modify following your HW

- TFA => - DDR_INIT to modify with your HW

- PLATFORM_DEF to modify with your HW

- UBOOT => -DDR.C to modify with your HW

and:

- Modify LS1046.c to disable (delete) PMIC related configuration AND I2C PCA configuration!!!!!

Then it can boot!

Hello,

So, I finally found where was the error without help of NXP.

To boot on LS1046 with different DDR4:

- RCW => modify following your HW

- TFA => - DDR_INIT to modify with your HW

- PLATFORM_DEF to modify with your HW

- UBOOT => -DDR.C to modify with your HW

and:

- Modify LS1046.c to disable (delete) PMIC related configuration AND I2C PCA configuration!!!!!

Then it can boot!

Hello,

My custom LS1088A board hangs in "Welcome to LS1088 BL31 Phase" just like yours.

Actually I used 5 DDRs soldered on board(1 as ECC) and I tried initiate DDR with MOCK DIMM way in ddr_init.c file. Which way did you boot up board?

Hello ufedor,

Our DDR4 design is fully validated by Code Warrior DDR tool.

Our DDR4 design passed the stress test.

But still not able to load U-Boot image. What other thing can be wrong?

Thank you

Just a note - it is reasonable to provide logs as text files (not pictures).

From the log it is possible to assume that DR SDRAM is not operational.

Have you used CodeWarrior QCVS DDR Tool to check/optimize the DDR controller settings?