- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

I see that each SerDes (1 and 2) have two PLLs each (1 and 2).

I don't see where in the manual you are able to select which PLL you want to use for which SerDes interface.

I see this register for example, but it doesn't seem to be tied to a particular SerDes

How do I assign PLL1 for SerDes1 and PLL2 for SerDes2 for example?

Thanks!

已解决! 转到解答。

Yes, PLL2 is used for all lanes in your example.

The muxer allows to use a single reference clock (SD1_REF_CLK1) for both PLL's. Yes, if you apply clocks to both inputs (SD1_REF_CLK1 and SD1_REF_CLK2), the muxer allows to select which clock is used as a reference for PLL2.

Regards,

Bulat

Your forgot to point out NXP device in the question.

For QorIQ devices the user can not explicitly select/assign PLLs for SERDES interfaces. All possible PLL to SERDES_lane assignments are made in hardware and depend on the SERDES configuration the user wants to use. SERDES configuration is defined by RCW configuration and happens when the processor comes out of reset.

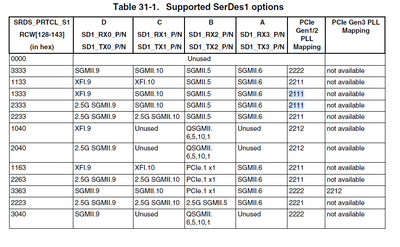

PLL to SERDES lanes mapping can be found in the reference manuals. See chapter "SerDes Module", first table of the chapter provides all possible configuration options of the SerDes. The first column shows RCW configuration options, the last column shows PLL's mapping to lanes. For example, mapping '2111' means PLL2 is assigned to lane #0, PLL1 is assigned lanes #1, #2, #3.

Regards,

Bulat

Ok I am using the LS1046A device.

So I want to run 1Gbps SGMII on SD1_RX0/TX0, SD1_RX1/TX1, and SD1_RX2/TX2.

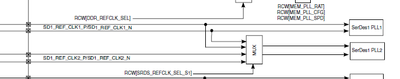

I can then choose RCW[128-143] = 3333, which gives me PLL2 for all lanes? And since I have a ref clock on both SD1_REF_CLK1 and SD1_REF_CLK2 inputs on my board I can select either one since there is a mux (see photo below)

Yes, PLL2 is used for all lanes in your example.

The muxer allows to use a single reference clock (SD1_REF_CLK1) for both PLL's. Yes, if you apply clocks to both inputs (SD1_REF_CLK1 and SD1_REF_CLK2), the muxer allows to select which clock is used as a reference for PLL2.

Regards,

Bulat